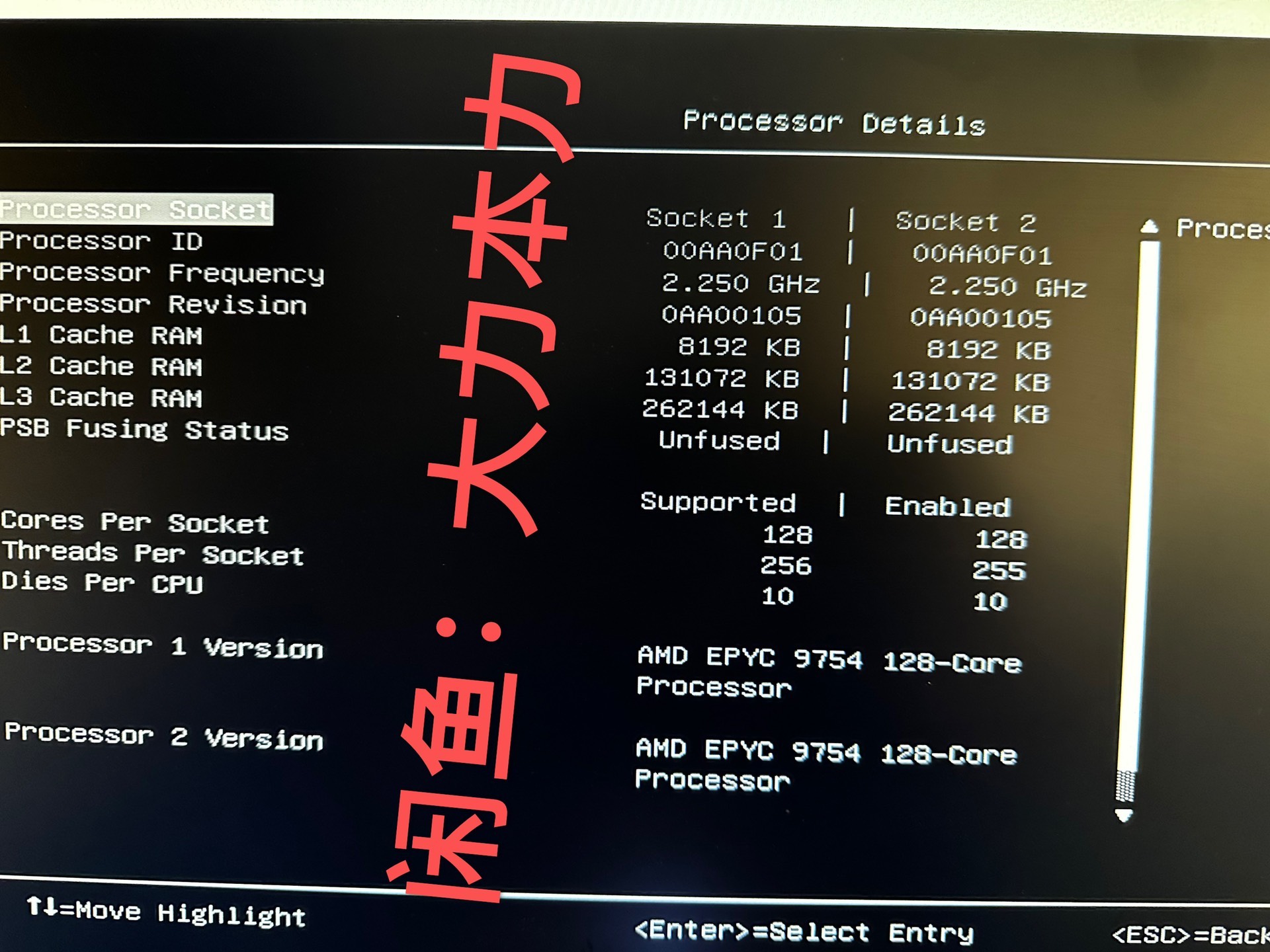

Não é bem assim, enche todos de uma vez quando dá miss em algum dado. A diferença é que depois que sai da L1/L2, se precisar de novo pode ir buscar na L3 ao invés de ir pra RAM.As instruções vão pros cores, conforme o tamanho e complexidade vai enchendo o cache L1, depois L2 e depois L3.

Update de scheduler deveria ter pq aplicações mais sensíveis à latência deveriam ir somente pro CCD com o 3D, caso contrário pegar dados da L3 3D vizinha vai ter uma latência bem maior. O mesmo pode ser dito pra aplicações que não são sensíveis à memória e que os dados já cabem de boas na L3 non-3D, deixar esses somente no CCD com clocks maiores seria mais eficiente.

Sem update isso vai ficar cagado, mas pelo menos o scheduler dos sistemas atuais já têm noção dos CCDs e sabem não deixar um mesmo processo com threads em 2 CCDs diferentes, quando possível.