You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

[TÓPICO DEDICADO] Coffee Lake / Coffee Lake Refresh

- Iniciador de Tópicos Fred Bastos

- Data de Início

Tava vendo essa imagem:

Socket novo pros mesmos 14nm+++? É isso mesmo?

Lga 1159 PINOS

Estava me coçando pra pegar um 9700k, mas acho que vou esperar a décima geração.Tava vendo essa imagem:

Socket novo pros mesmos 14nm+++? É isso mesmo?

Melhor IPC, mais threads e sem aquelas falhas de segurança nojentas.

Acabei de ler sobre a décima geração aqui https://wccftech.com/intel-10th-gen-comet-lake-desktop-cpu-lineup-leak-lga-1159-socket-rumor/

É boato mas os dados batem com o que se espera para o ano que vem.

Quando esses chegarem no mercado acaba o mimimi

É boato mas os dados batem com o que se espera para o ano que vem.

Quando esses chegarem no mercado acaba o mimimi

Se chegar com os preços que o amigo postou, acho que muita gente vai abandonar os ryzenTava vendo essa imagem:

Socket novo pros mesmos 14nm+++? É isso mesmo?

Intel diz EUV pronto, desafiador

https://www.eetimes.com/document.asp?doc_id=1334769

SAN JOSE, Califórnia - A litografia ultravioleta extrema (EUV) está “pronta para ser introduzida… e funcionando em volume para o desenvolvimento de tecnologia”, disse o chefe do programa EUV da Intel. Mas os engenheiros ainda enfrentam vários desafios para aproveitar os sistemas complexos e caros para fabricar chips de ponta em alto volume, disse ela.

Britt Turkot, um colega e diretor da EUV na Intel, disse que os sistemas do tamanho de uma sala estão rodando em sua gigante Portland, Oregon, fab. Ela não diria como ou se o EUV será usado para os produtos de 10 nm da empresa em operação agora ou para o nó planejado de 7 nm.

A Intel estava entre as empresas de semicondutores que ajudaram a desenvolver a tecnologia há mais de duas décadas, mas é uma das últimas a confirmar seu uso. No ano passado, os rivais Samsung e TSMC anunciaram separadamente que estavam usando nódulos de 7 nm usando sistemas EUV para imprimir seus melhores recursos.

No entanto, em uma indicação dos desafios ainda pela frente, duas fontes disseram que o N7 + da TSMC está usando o EUV para apenas quatro camadas de metal. Isso significa que ainda requer o uso de padrões duplos com steppers de imersão tradicionais para algumas camadas de metal.

A decisão da TSMC é provavelmente "sobre o rendimento, quantas máquinas EUV eles têm, e custam trade-offs ... A Samsung pode ter investido mais em máquinas EUV", disse uma fonte que pediu para não ser identificada.

Os sistemas custam cerca de US $ 150 milhões cada, e vários são necessários para uma linha de produção comercial.

"Nós realmente implantamos padrões duplos em muitas camadas", disse uma porta-voz da TSMC, que se recusou a comentar sobre quantas camadas de metal a fundição usa o EUV para seu nó N7 +. “A decisão de usar padrões duplos de imersão versus EUV é baseada em várias considerações. O custo e a maturidade da EUV versus a imersão definitivamente é importante ”.

Separadamente, uma fonte disse que a Samsung está prejudicando agressivamente os preços do seu nó de 7-nm com o EUV, oferecendo a algumas startups uma máscara completa para menos de uma máscara multi-camada (MLM) definida em seu rival. A TSMC introduziu os conjuntos de máscaras de MLM em 2007 para reduzir os custos de pequenas tiragens. Dizem que são cerca de 60% do custo de um conjunto completo de máscaras.

A Samsung se recusou a comentar sobre seus preços de fundição ou como ela usa o EUV. Um executivo da Samsung especulou que a Intel estava atrasada em seu processo de 10 nm, em parte devido ao seu uso ambicioso de estruturas de contato por portas ativas (COAG) . Samsung vai gradualmente se mover em direção COAG, disse ele, recusando-se a dar detalhes.

Em um blog recente, o diretor de engenharia da Intel, Murthy Renduchintala, caracterizou o nó de 10 nm da empresa como, de certa forma, ambicioso. Mas ele disse que os chips que o usam agora estão em produção e que o trabalho em um nó de 7 nm está progredindo bem.

Em entrevista ao EE Times, Turkot disse que a Intel ainda não decidiu quantas camadas de metal serão usadas com o EUV, acrescentando que escolher quais camadas aplicar o EUV é tanto arte quanto ciência. "Custo por camada não é um cálculo direto - não é economia direta."

Por exemplo, uma única exposição EUV às vezes pode reduzir a contagem de máscaras para uma camada em uma proporção de até 5: 1. No entanto, a padronização dupla com steppers de imersão pode ajudar a reduzir os erros de colocação de bordas, observou ela.

A confiabilidade do sistema é outra variável impactando o custo. A Intel atualmente relata o tempo de atividade do sistema de cerca de 75% a 80% para seus sistemas EUV. "O número não é onde precisa ser de longo prazo, mas é bom o suficiente para a introdução", disse Turkot. "Queremos que seja como uma imersão hoje, nos anos 90".

A boa notícia é que o tempo de inatividade é "mais previsível", disse ela. “Era extremamente imprevisível no passado e [dificultava] sustentar uma linha de produtos e executar uma linha de volume para o desenvolvimento.”

A maioria dos avanços em confiabilidade veio da “compreensão dos tipos típicos de tempo de inatividade não surpreendente das ferramentas e da criação de especialistas para diagnosticar rapidamente os problemas e implementar as soluções necessárias em toda a frota”.

Grande parte do foco no throughput EUV tem sido o poder da fonte de luz. É um componente crítico e complexo que gera luz ao atingir uma gota de estanho derretido com um laser. No entanto, na prática, Turkot sugeriu que outro componente EUV - o coletor de luz - está se tornando um elemento mais importante no rendimento do sistema e no tempo de operação.

A Intel tem sistemas EUV funcionando com fontes de energia que variam de 205 W a 285 W. No nível do wafer, "todos eles estão dando o mesmo poder por causa do coletor", disse ela. dia como o coletor degrada. ”

Novamente, a boa notícia é que “há uma clara linha de visão para a meta [ASML] de direcionar energia de fonte de exposição e tempo de inatividade [fazendo] substituição de coletor… Há uma sobrecarga fixa removendo e substituindo o coletor e trazendo o sistema de volta e reduzindo a taxa de contaminação. A ASML está fazendo um grande progresso ”.

Separadamente, a ASML está agora fornecendo filmes de proteção chamados películas. Eles mantêm as bolachas seguras contra partículas finas que poderiam contaminá-las e reduzir os rendimentos.

Olhando para o futuro, os pesquisadores estão preocupados que erros aleatórios chamados de estocásticosque quebram ou não completem uma linha traçada com um sistema EUV limitarão seu uso a 5 nm ou mais. Turkot expressou otimismo de que as melhorias necessárias virão em ambos os efeitos com a luz EUV e resistir à química.

“O ruído de disparo fotônico pode ser superado por exposições maiores [de luz]. Os aspectos químicos resistentes exigirão uma quantidade significativa de trabalho pela comunidade de resistência.

"Eles têm que entender as respostas químicas de materiais em elétrons secundários e íons criados por uma exposição de alta energia ... Não há consenso ainda sobre uma métrica para material estocástico", disse ela, apesar de muitos trabalhos escritos sobre o tema.

“Na introdução [EUV], eu não espero que [stochastics] tenha um impacto sobre o rendimento, mas quando você olha para extensões EUV [para 5 nm e além], é um potencial limitador. No momento em que chegarmos lá, espero que haja compreensão suficiente dos fornecedores de resistência que podem ser contornados. A chave está trabalhando nisso agora.

Turkot lembrou como, ao ver os sistemas EUV de hoje, “o tamanho e a complexidade do sistema eram impressionantes”, e os sistemas de próxima geração para 3 nm e além são muito maiores.

No geral, ela descreveu como “muito gratificante” ter a chance de trabalhar nos sistemas gigantescos necessários para impulsionar a tecnologia de semicondutores.

“Está sendo feito um grande esforço para depurar o EUV, como qualquer nova plataforma. Toda a intenção é que, quando chegar a hora da produção, não podemos dizer a diferença - é uma transição perfeita ”.

https://www.eetimes.com/document.asp?doc_id=1334769

SAN JOSE, Califórnia - A litografia ultravioleta extrema (EUV) está “pronta para ser introduzida… e funcionando em volume para o desenvolvimento de tecnologia”, disse o chefe do programa EUV da Intel. Mas os engenheiros ainda enfrentam vários desafios para aproveitar os sistemas complexos e caros para fabricar chips de ponta em alto volume, disse ela.

Britt Turkot, um colega e diretor da EUV na Intel, disse que os sistemas do tamanho de uma sala estão rodando em sua gigante Portland, Oregon, fab. Ela não diria como ou se o EUV será usado para os produtos de 10 nm da empresa em operação agora ou para o nó planejado de 7 nm.

A Intel estava entre as empresas de semicondutores que ajudaram a desenvolver a tecnologia há mais de duas décadas, mas é uma das últimas a confirmar seu uso. No ano passado, os rivais Samsung e TSMC anunciaram separadamente que estavam usando nódulos de 7 nm usando sistemas EUV para imprimir seus melhores recursos.

No entanto, em uma indicação dos desafios ainda pela frente, duas fontes disseram que o N7 + da TSMC está usando o EUV para apenas quatro camadas de metal. Isso significa que ainda requer o uso de padrões duplos com steppers de imersão tradicionais para algumas camadas de metal.

A decisão da TSMC é provavelmente "sobre o rendimento, quantas máquinas EUV eles têm, e custam trade-offs ... A Samsung pode ter investido mais em máquinas EUV", disse uma fonte que pediu para não ser identificada.

Os sistemas custam cerca de US $ 150 milhões cada, e vários são necessários para uma linha de produção comercial.

"Nós realmente implantamos padrões duplos em muitas camadas", disse uma porta-voz da TSMC, que se recusou a comentar sobre quantas camadas de metal a fundição usa o EUV para seu nó N7 +. “A decisão de usar padrões duplos de imersão versus EUV é baseada em várias considerações. O custo e a maturidade da EUV versus a imersão definitivamente é importante ”.

Separadamente, uma fonte disse que a Samsung está prejudicando agressivamente os preços do seu nó de 7-nm com o EUV, oferecendo a algumas startups uma máscara completa para menos de uma máscara multi-camada (MLM) definida em seu rival. A TSMC introduziu os conjuntos de máscaras de MLM em 2007 para reduzir os custos de pequenas tiragens. Dizem que são cerca de 60% do custo de um conjunto completo de máscaras.

A Samsung se recusou a comentar sobre seus preços de fundição ou como ela usa o EUV. Um executivo da Samsung especulou que a Intel estava atrasada em seu processo de 10 nm, em parte devido ao seu uso ambicioso de estruturas de contato por portas ativas (COAG) . Samsung vai gradualmente se mover em direção COAG, disse ele, recusando-se a dar detalhes.

Em um blog recente, o diretor de engenharia da Intel, Murthy Renduchintala, caracterizou o nó de 10 nm da empresa como, de certa forma, ambicioso. Mas ele disse que os chips que o usam agora estão em produção e que o trabalho em um nó de 7 nm está progredindo bem.

Em entrevista ao EE Times, Turkot disse que a Intel ainda não decidiu quantas camadas de metal serão usadas com o EUV, acrescentando que escolher quais camadas aplicar o EUV é tanto arte quanto ciência. "Custo por camada não é um cálculo direto - não é economia direta."

Por exemplo, uma única exposição EUV às vezes pode reduzir a contagem de máscaras para uma camada em uma proporção de até 5: 1. No entanto, a padronização dupla com steppers de imersão pode ajudar a reduzir os erros de colocação de bordas, observou ela.

A confiabilidade do sistema é outra variável impactando o custo. A Intel atualmente relata o tempo de atividade do sistema de cerca de 75% a 80% para seus sistemas EUV. "O número não é onde precisa ser de longo prazo, mas é bom o suficiente para a introdução", disse Turkot. "Queremos que seja como uma imersão hoje, nos anos 90".

A boa notícia é que o tempo de inatividade é "mais previsível", disse ela. “Era extremamente imprevisível no passado e [dificultava] sustentar uma linha de produtos e executar uma linha de volume para o desenvolvimento.”

A maioria dos avanços em confiabilidade veio da “compreensão dos tipos típicos de tempo de inatividade não surpreendente das ferramentas e da criação de especialistas para diagnosticar rapidamente os problemas e implementar as soluções necessárias em toda a frota”.

Grande parte do foco no throughput EUV tem sido o poder da fonte de luz. É um componente crítico e complexo que gera luz ao atingir uma gota de estanho derretido com um laser. No entanto, na prática, Turkot sugeriu que outro componente EUV - o coletor de luz - está se tornando um elemento mais importante no rendimento do sistema e no tempo de operação.

A Intel tem sistemas EUV funcionando com fontes de energia que variam de 205 W a 285 W. No nível do wafer, "todos eles estão dando o mesmo poder por causa do coletor", disse ela. dia como o coletor degrada. ”

Novamente, a boa notícia é que “há uma clara linha de visão para a meta [ASML] de direcionar energia de fonte de exposição e tempo de inatividade [fazendo] substituição de coletor… Há uma sobrecarga fixa removendo e substituindo o coletor e trazendo o sistema de volta e reduzindo a taxa de contaminação. A ASML está fazendo um grande progresso ”.

Separadamente, a ASML está agora fornecendo filmes de proteção chamados películas. Eles mantêm as bolachas seguras contra partículas finas que poderiam contaminá-las e reduzir os rendimentos.

Olhando para o futuro, os pesquisadores estão preocupados que erros aleatórios chamados de estocásticosque quebram ou não completem uma linha traçada com um sistema EUV limitarão seu uso a 5 nm ou mais. Turkot expressou otimismo de que as melhorias necessárias virão em ambos os efeitos com a luz EUV e resistir à química.

“O ruído de disparo fotônico pode ser superado por exposições maiores [de luz]. Os aspectos químicos resistentes exigirão uma quantidade significativa de trabalho pela comunidade de resistência.

"Eles têm que entender as respostas químicas de materiais em elétrons secundários e íons criados por uma exposição de alta energia ... Não há consenso ainda sobre uma métrica para material estocástico", disse ela, apesar de muitos trabalhos escritos sobre o tema.

“Na introdução [EUV], eu não espero que [stochastics] tenha um impacto sobre o rendimento, mas quando você olha para extensões EUV [para 5 nm e além], é um potencial limitador. No momento em que chegarmos lá, espero que haja compreensão suficiente dos fornecedores de resistência que podem ser contornados. A chave está trabalhando nisso agora.

Turkot lembrou como, ao ver os sistemas EUV de hoje, “o tamanho e a complexidade do sistema eram impressionantes”, e os sistemas de próxima geração para 3 nm e além são muito maiores.

No geral, ela descreveu como “muito gratificante” ter a chance de trabalhar nos sistemas gigantescos necessários para impulsionar a tecnologia de semicondutores.

“Está sendo feito um grande esforço para depurar o EUV, como qualquer nova plataforma. Toda a intenção é que, quando chegar a hora da produção, não podemos dizer a diferença - é uma transição perfeita ”.

Tava vendo essa imagem:

Socket novo pros mesmos 14nm+++? É isso mesmo?

M A K E M O R E C O R E S!

Tava vendo essa imagem:

Socket novo pros mesmos 14nm+++? É isso mesmo?

Agora que eu notei uma coisa, tem um Core i3 com 4 cores com o TPD de 91 watts. Literalmente housefires.

Ataques de canal lateral em processadores incorporados

https://www.eetimes.com/author.asp?section_id=36&doc_id=1334783

Enclaves seguros e raiz de confiança não são suficientes. As vulnerabilidades de hardware afetam a segurança de sistemas automotivos, médicos e de IoT.

Em janeiro de 2018, pesquisadores de segurança de computadores revelaram duas vulnerabilidades críticas de processador que programas mal-intencionados poderiam explorar para vazar dados seguros: o Meltdown e o Specter .

A comunidade de engenharia e o público em geral estão acostumados a vulnerabilidades de software que exigem atualizações frequentes de aplicativos ou instalação de patches do sistema operacional. Estes eram diferentes - o hardware era o culpado e o hardware não é barato de atualizar.

A única abordagem prática é lançar um novo software que, ao custo de tornar o sistema mais lento e menos eficiente em termos de energia, mascara funções de hardware vulneráveis ou evita seu uso. Meltdown e Spectre provocaram uma série de investigações sobre segurança de hardware.

Os pesquisadores já revelou inúmeros mais vulnerabilidades, incluindo Foreshadow , ZombieLoad , RIDL, e Fallout . Essas falhas de hardware comprometem a segurança de computadores pessoais, smartphones e até mesmo da nuvem.

Figura 1: Um processo atacante extrai dados secretos de um processo vítima através de um canal lateral microarquitetural baseado em um buffer de preenchimento de linha (LFB). Os processos de vítimas e invasores estão em diferentes domínios de segurança. (Fonte: S. van Schaik e outros, RIDL: Rogue In-Flight Data Load)

Artigo completo: https://www.eetimes.com/author.asp?section_id=36&doc_id=1334783

https://www.eetimes.com/author.asp?section_id=36&doc_id=1334783

Enclaves seguros e raiz de confiança não são suficientes. As vulnerabilidades de hardware afetam a segurança de sistemas automotivos, médicos e de IoT.

Em janeiro de 2018, pesquisadores de segurança de computadores revelaram duas vulnerabilidades críticas de processador que programas mal-intencionados poderiam explorar para vazar dados seguros: o Meltdown e o Specter .

A comunidade de engenharia e o público em geral estão acostumados a vulnerabilidades de software que exigem atualizações frequentes de aplicativos ou instalação de patches do sistema operacional. Estes eram diferentes - o hardware era o culpado e o hardware não é barato de atualizar.

A única abordagem prática é lançar um novo software que, ao custo de tornar o sistema mais lento e menos eficiente em termos de energia, mascara funções de hardware vulneráveis ou evita seu uso. Meltdown e Spectre provocaram uma série de investigações sobre segurança de hardware.

Os pesquisadores já revelou inúmeros mais vulnerabilidades, incluindo Foreshadow , ZombieLoad , RIDL, e Fallout . Essas falhas de hardware comprometem a segurança de computadores pessoais, smartphones e até mesmo da nuvem.

Figura 1: Um processo atacante extrai dados secretos de um processo vítima através de um canal lateral microarquitetural baseado em um buffer de preenchimento de linha (LFB). Os processos de vítimas e invasores estão em diferentes domínios de segurança. (Fonte: S. van Schaik e outros, RIDL: Rogue In-Flight Data Load)

Artigo completo: https://www.eetimes.com/author.asp?section_id=36&doc_id=1334783

Tava vendo essa imagem:

Socket novo pros mesmos 14nm+++? É isso mesmo?

O que uma concorrência que coça o cangote não faz, hein?!

Se chegar com os preços que o amigo postou, acho que muita gente vai abandonar os ryzen

Abandonar não irão até pq os Ryzen 3000 chegaram agora e possa ser que BIOS melhorem a performance do CPU (ainda não desempenha tanto por conta de BIOS porcas), fora que por 499 a AMD tem um CPU de 12/24 contra um possível 10/20 da Intel, mas é aquilo, às vezes mais núcleos não significam sempre melhor desempenho. Gosto que a Intel comece a parar de ter nariz empinado e corra atrás do monopólio quad-core que ela colocou mto por culpa tmb da AMD em ter parado no tempo, só que é foda o cara que gosta de Intel ter que NOVAMENTE trocar de mobo pq a Intel inventa que é necessário mais 8, 9 10 pinagens no soquete pro CPU funcionar. Nem o mais fanboy do planeta atura isso.

EDIT:

Processador de PC de 10 nm da Ice Tips da Intel

https://www.eetimes.com/document.asp?doc_id=1334158&page_number=2

Intel revela 10 processos de 22 nm

https://www.eetimes.com/document.asp?doc_id=1331531&page_number=2#

Kanter elogiou o avanço do transistor COAG da Intel. No entanto, até que a empresa publique como ela fabrica dispositivos COAG, não será claro se ela pode usar o design como uma nova maneira de otimizar a resistência de contato e, assim, diferenciar seus processos.

Visão da Intel sobre a Revolução Chiplet

Ramune Nagisetty está ajudando a Intel a estabelecer seu lugar em um novo ecossistema da indústria centrado em chiplets

https://spectrum.ieee.org/tech-talk/semiconductors/processors/intels-view-of-the-chiplet-revolution

Chiplets são uma maneira de fazer sistemas que executam muito como se fossem todos um chip, apesar de serem compostos por vários chips menores. Eles são amplamente vistos como uma parte do plano da indústria de computação para manter os sistemas funcionando melhor e melhor, apesar do fato de que o tradicional escore Lei de Moore está chegando ao fim . Os defensores dizem que os benefícios incluirão sistemas mais especializados e maior rendimento, entre outras coisas. Mas o mais importante, eles podem levar a uma grande mudança na indústria de semicondutores, onde o produto final pode se tornar um pequeno e especializado chiplet destinado a ser combinado no mesmo pacote com um processador de uso geral e muitos outros chiplets especiais. Ramune NagisettyEngenheiro principal e diretor de integração de processos e produtos do grupo de desenvolvimento de tecnologia da Intel em Oregon, tem trabalhado para ajudar a desenvolver um ecossistema chiplet de toda a indústria. Ela disse ao IEEE Spectrum sobre isso e as tecnologias da Intel envolvidas em 21 de março de 2019.

Ramune Nagisetty em:

Quais são os chiplets?

chiplets são e diria por que eles estão se tornando importantes?

Ramune Nagisetty: Um chiplet é uma peça física de silício. Ele encapsula um subsistema IP (propriedade intelectual). E foi projetado para integrar-se a outros chiplets por meio da integração em nível de pacote, normalmente por meio da integração avançada de pacotes e do uso de interfaces padronizadas.

Por que eles estão se tornando importantes? É porque não existe uma abordagem única que funcione mais. Temos uma explosão nos diferentes tipos de computação e cargas de trabalho, portanto, há várias arquiteturas diferentes que estão surgindo para oferecer suporte a esses diferentes tipos de modelos de computação. Basicamente, a integração heterogênea da melhor tecnologia é uma maneira de continuar as tendências de desempenho da lei de Moore.

IEEE Spectrum: Quando você fala sobre tecnologias heterogêneas, você também quer dizer materiais semicondutores além do silício?

Nagisetty: Eu diria que não é necessariamente apenas silício, haverá outros tipos de tecnologias semicondutoras também. Você pode incluir coisas como tecnologias baseadas em germânio ou III-Vs. No futuro, teremos tipos mais variados de tecnologias de semicondutores. Hoje, é principalmente silício.

Mesmo com apenas chiplets baseados em silício, eles certamente estarão em diferentes nós de tecnologia. Eles geralmente são ajustados para melhor desempenho em diferentes áreas - seja digital, analógica, RF ou, por exemplo, tecnologias de memória.

A memória de alta largura de banda, ou HBM, é essencialmente um dos primeiros pontos de prova da integração em pacotes de silício heterogêneo. A memória é essencialmente o primeiro tipo de integração heterogênea que está realmente ganhando força usando a embalagem avançada.

IEEE Spectrum: A maneira da Intel conectar os chiplets é chamada de ponte integrada de interconexão de vários terminais . Por favor, diga-nos o que é e como funciona.

Nagisetty: Você pode pensar nisso como uma ponte de alta densidade conectando dois chiplets juntos, que é essencialmente a melhor maneira de descrevê-lo. Eu acho que muitas pessoas estão familiarizadas com a idéia de usar um interposer de silício como um substrato de embalagem avançado. [Os interposers de silício são substratos de silício com interconexões densas e vias de silício integradas nelas. Eles permitem conexões de alta largura de banda entre os chips.]

Imagem: Intel

Um EMIB [círculo] conecta-se a chips dentro do mesmo pacote usando interconexões de alta densidade. Os solavancos de conexão que ligam os chips ao EMIB têm um pitch muito mais fino do que os solavancos normais [bottom left].

O que é um EMIB é, essencialmente, um pedaço muito pequeno de um interposer de silício que possui interconexões de densidade muito alta e o que chamamos de microbumps em uma densidade muito maior do que você encontraria em um substrato de embalagem padrão. [Microbombas são pequenas bolas de solda que ligam um chip a outro chip ou a interconexões de alta densidade de um pacote.]

Esse EMIB ou bridge é essencialmente incorporado em um substrato de embalagem padrão. Com o EMIB, você é essencialmente capaz de obter a maior densidade de interconexão exatamente onde precisa e, em seguida, pode usar um substrato de embalagem padrão para o restante da interconexão.

Há muitos benefícios em fazer isso dessa maneira. Um deles é custado porque o custo de um interposer de silício é proporcional à área desse interposer. Então, neste caso, localizamos realmente a interconexão de alta densidade na área onde é necessária. E também há benefícios em termos de perda geral de inserção - a atenuação do sinal devido às propriedades do material - usando um substrato de embalagem padrão em vez de um intermediário de silício.

IEEE Spectrum: O que a Intel usou o EMIB até agora?

Nagisetty: A Intel na verdade tem várias soluções chiplet demonstradas, e eu gostaria de falar sobre cada uma delas, porque acho que ajuda a esclarecer o que eu acho que são as três direções diferentes que os chiplets seguirão.

A Intel tem duas soluções baseadas no EMIB atualmente, mas são muito diferentes. O primeiro é o Kaby Lake-G , e é basicamente onde integramos uma GPU AMD Radeon e uma memória de alta largura de banda [HBM] com nosso chip de CPU. Usamos o EMIB para integrar a GPU e a HBM, usando uma interface da HBM dentro do pacote. E então usamos PCI Express , que é uma interface padrão de placa de circuito, dentro do pacote para integrar a GPU e a CPU.

O que é realmente interessante sobre essa solução é que estamos usando silício desenvolvido externamente a partir de várias fundições e estamos usando interfaces padrão da indústria comuns - HBM e PCI Express - para criar um produto de primeira classe. Nesse caso, pegamos um componente (GPU com HBM) que era capaz de ficar sozinho em uma placa e o integramos em um pacote. O PCI Express foi projetado para enviar sinais por longas distâncias mais típicas de uma placa. Quando você coloca dentro de um pacote, na verdade não é necessariamente uma solução ideal, mas é uma solução rápida porque estamos utilizando interfaces que já existem na indústria.

IEEE Spectrum: Qual a vantagem desta integração?

Nagisetty: Neste caso, o que ganhamos é um enorme fator de forma, ou tamanho, melhoria. Para jogos móveis, caber dentro de um design de laptop é realmente importante. Essencialmente, você está sempre negociando fator de forma, poder e desempenho um do outro. Portanto, neste caso, ele é realmente otimizado para ter uma solução de primeira classe no menor tamanho possível.

IEEE Spectrum: Qual é o outro exemplo chiplet que você queria descrever?

Nagisetty: A próxima coisa que eu gostaria de falar é sobre o FPGA Stratix 10, que na verdade foi a primeira demonstração da solução EMIB da Intel. O Stratix 10 tem um FPGA da Intel no centro dele. E então tem seis chiplets em torno do FPGA. Quatro deles são chiplets transceptores de alta velocidade, e dois deles são chiplets de memória de alta largura de banda, e todos eles são montados em um pacote. Este exemplo integra seis diferentes nós de tecnologia de três fundições diferentes; então é mais uma prova de interoperabilidade em termos de diferentes fundições.

Imagem: Intel

A Intel Stratix 10 é um excelente exemplo do uso de EMIBs para conectar chiplets em um pacote.

A segunda coisa é que ele usa uma interface die-to-die padrão da indústria chamada AIB, que é o Advanced Interface Bus da Intel. Ele foi criado para este produto e é essencialmente a semente de um padrão de mercado para uma interconexão de lógica para lógica de alta largura de banda dentro do pacote. Portanto, o HBM é o primeiro padrão para integração de memória e o AIB é o primeiro padrão para integração lógica.

O AIB é uma interface que pode ser usada com a solução EMIB da Intel e com soluções concorrentes, como interpositores de silício. Mas o que é realmente bom nessa interface e o FPGA no centro desse ecossistema é a abordagem de combinação e combinação que é possível. Há muitas empresas diferentes e muitas universidades diferentes que estão criando chiplets usando o AIB por meio de um esforço patrocinado pelo programa CHIPS ( Integração Heterogênea Comum e Reutilização de Estratégias de IP ) da DARPA .

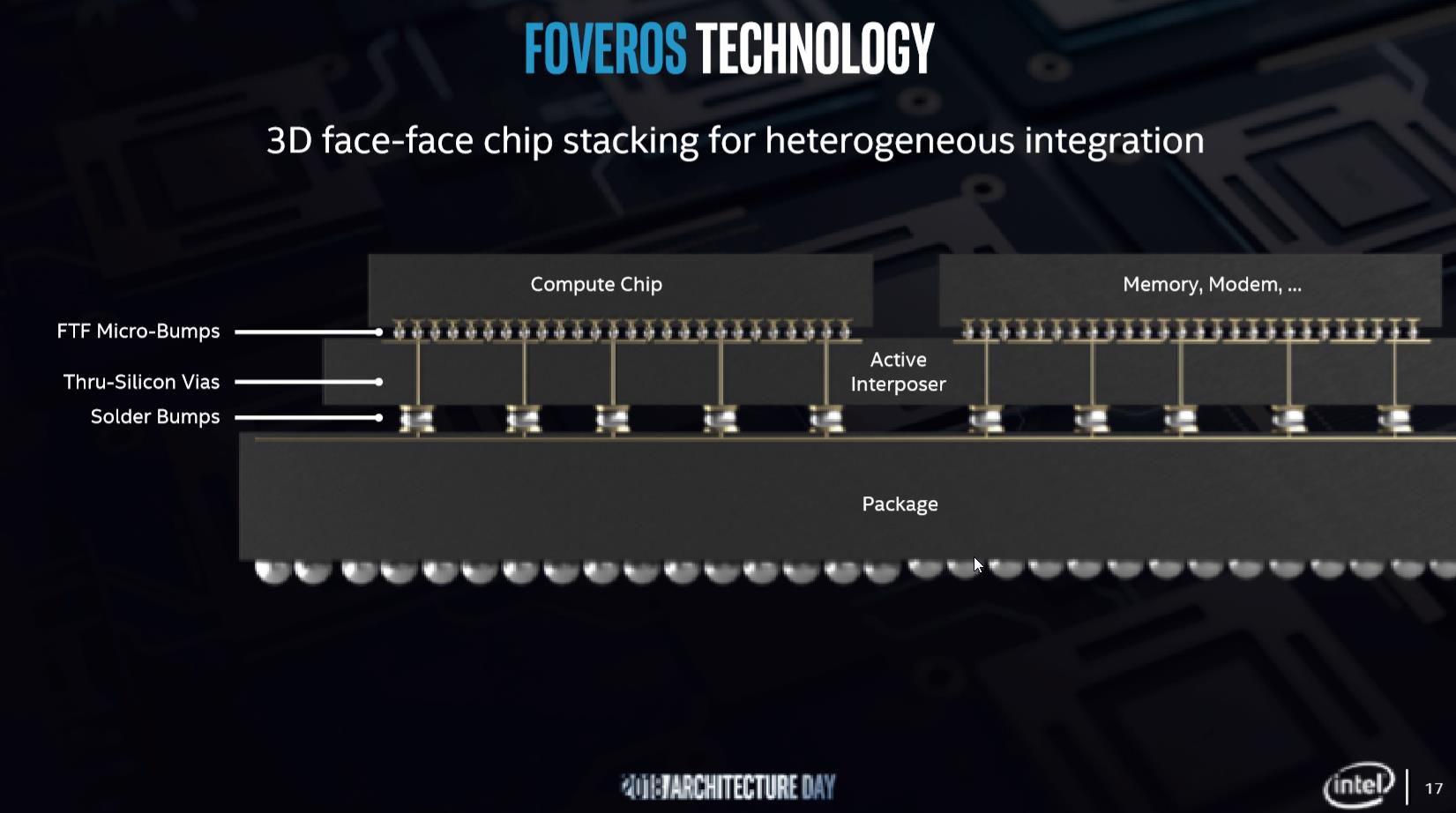

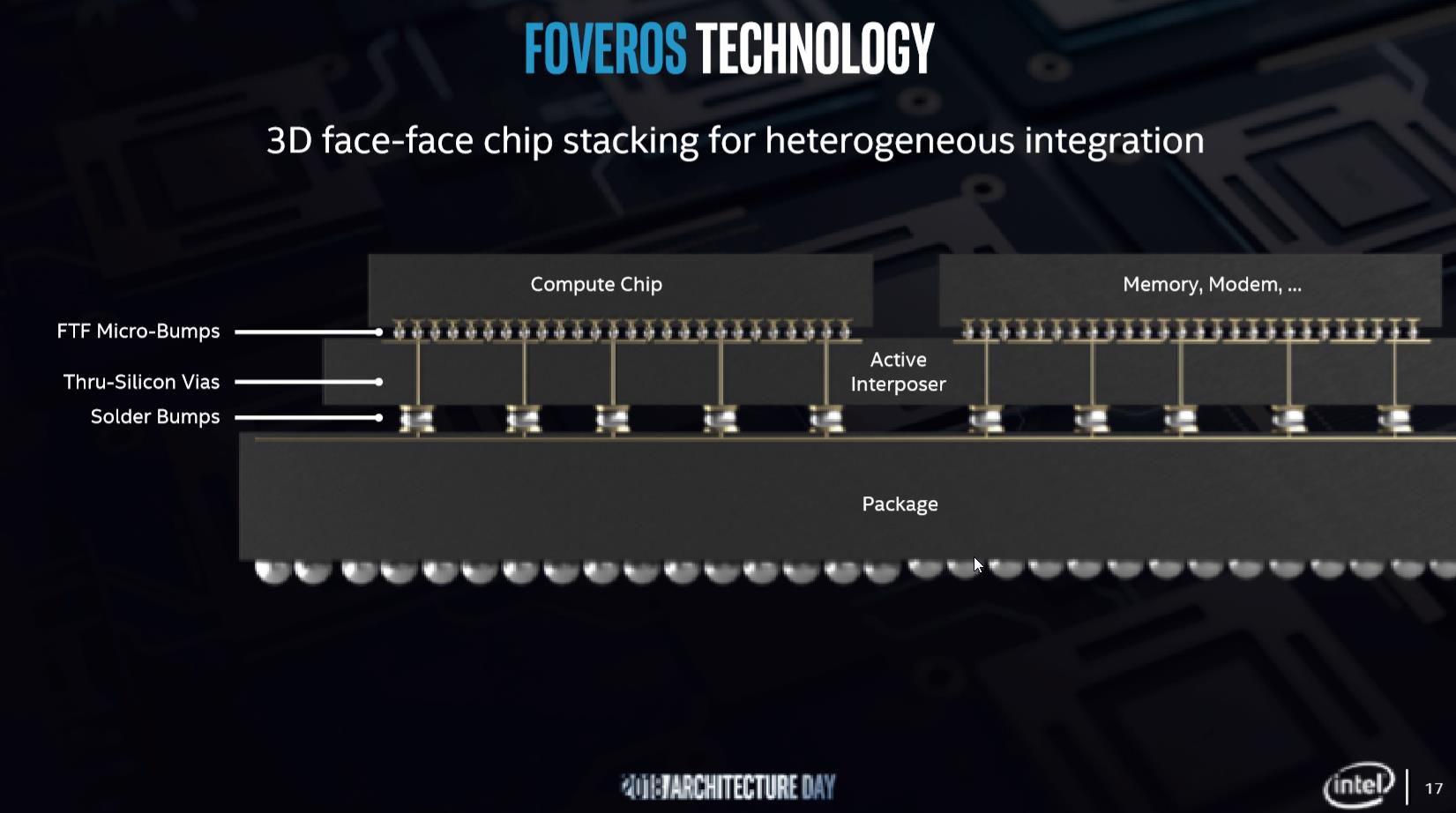

Foveros , da Intel , que é o nosso empilhamento de lógico de lógica lógica, e que foi falado pela primeira vez em dezembro e depois o produto, chamado Lakefield, foi anunciado em janeiro na CES . Esta é a integração do chiplet, mas em vez do empilhamento horizontal, é o empilhamento vertical.

Esse tipo de integração permite que você obtenha uma largura de banda extremamente alta entre os dois chiplets. Mas ele é baseado em interfaces proprietárias internas e os dois morrem são essencialmente co-projetados porque precisam ser planejados juntos para gerenciar coisas como distribuição de energia e térmicas.

Para o empilhamento lógico de matrizes lógicas, provavelmente será um prazo muito maior antes de vermos os padrões emergentes na área da indústria, porque os moldes são essencialmente co-projetados juntos. O empilhamento de memória no topo da lógica provavelmente será o primeiro lugar onde qualquer tipo de padrão se desenvolve para o empilhamento tridimensional.

/ P1274 é o nome da Intel para o seu processo de 10nm de alto desempenho. P1222 é o seu processo 22FFL (22nm, FinFET, Low Power), que é otimizado para vazamento de corrente muito menor. Assim como a conexão Foveros entre os módulos de computação e de E / S, o produto usará a memória empacotada convencional em pacote-em-pacote.

O smicrobumps da Enlarge / Foveros permitem comunicação cara a cara entre os dados.

Diagrama de vista lateral da tecnologia de empacotamento Foveros 3D da Intel. (Fonte: Intel)

IEEE Spectrum: Ao projetar para chips empilhados, quais são algumas das coisas que você deve observar?

Nagisetty: Problemas térmicos são os principais. Como você pode imaginar, o empilhamento de folhas exacerba qualquer tipo de problema térmico. Então, precisamos fazer um planejamento cuidadoso do piso para acomodar os pontos de acesso térmicos. Também precisamos considerar a arquitetura de todo o sistema. As implicações do uso do empilhamento 3D levarão até as decisões arquiteturais, não apenas a arquitetura física, mas toda a CPU ou GPU e a arquitetura do sistema.

IEEE Spectrum: Que tipos de padrões ainda são necessários para avançar os chiplets?

Nagisetty: Os padrões do setor em relação aos testes são realmente importantes. Normalmente, fazemos testes com peças totalmente empacotadas. Precisamos ser capazes de colocar “bons dados conhecidos” (chiplets que sabemos que funcionam) dentro de um pacote, para que não acabemos inadvertidamente com a queda do rendimento devido a um único chiplet ser ruim e os outros chiplets serem bons. Então, precisamos de uma estratégia para bons dados conhecidos e precisamos de uma estratégia para teste.

Outra coisa que precisamos é de suporte a vários fornecedores para gerenciamento de energia e térmica. Isso significa ser capaz de ter ganchos em todos os chiplets integrados para gerenciar energia e gerenciar térmicas.

E, em termos de intraoperabilidade elétrica, a AIB - a interface que lançamos em julho passado - é realmente apenas um padrão no que chamamos de nível PHY, que é a interface física e elétrica. Mas precisamos ter padrões que também percorram os protocolos da camada superior.

Eu acho que o último, e pode parecer óbvio, é um padrão mecânico - literalmente a colocação de microbombas e roteamento entre padrões de necessidades de microbombas para suportar a interoperabilidade.

Foto: Intel

Ramune Nagisetty

IEEE Spectrum: Você pode nos contar um pouco mais sobre o problema do “conhecido bom die” e como os testes terão que ser diferentes com os chiplets?

Nagisetty: Bem, é realmente muito diferente, porque a capacidade de garantir completamente o Known Good Die é geralmente baseada em testes a quente de uma parte empacotada. Portanto, com os chiplets agora você tem que ser capaz de testar essencialmente os chips mortos antes de serem empacotados - no mesmo nível de capacidade. É mais fácil testar peças empacotadas, facilitar a entrega de energia e assim por diante. Quando você faz isso com o dado desencapado, você tem desafios com sondagem, porque você tem os pads extras que você precisa para configurar as sondas.

A outra coisa é que qualquer coisa que você precise para testar se ela morrer independentemente, seja um relógio ou qualquer outro tipo de garantia para poder testar completamente cada chiplet, precisa ser projetada no chiplet. Os chiplets não podem ser co-dependentes uns dos outros para testá-los. Eles precisam ser totalmente testados individualmente antes de serem empacotados.

Há trabalho acontecendo nesta área. E é extremamente importante porque, você pode imaginar, no momento em que você tem uma parte embalada com muitos chiplets dentro dele, há muito valor nessa parte empacotada. E se qualquer um desses chiplets for ruim e não for redundante ou consertável, então você essencialmente descartou muitos outros chiplets que têm valor.

IEEE Spectrum: Não é um dos benefícios propostos de chiplets que eles levam a um melhor rendimento, porque eles são fisicamente menores e, portanto, menos propensos a erros?

IEEE Spectrum: Como o chiplets mudará a maneira como as coisas são projetadas?

Nagisetty: A integração de memória de alta largura de banda é realmente o primeiro ponto de prova, e já está sendo amplamente usada em GPUs e também com processadores AI em sistemas de alto desempenho. Portanto, neste caso, as chiplets e a integração de pacotes de memória já estão mudando a maneira como os chips são projetados e integrados.

Co-design de chiplets certamente será uma área importante que se desenvolverá. O que eu realmente acho que vai acontecer é que teremos vários fornecedores fornecendo chiplets. E então, quais são os limites arquitetônicos? E como projetamos os melhores produtos baseados nos blocos de construção que temos? Nós estamos realmente apenas no começo do que eu acho que é uma revolução. Um novo ecossistema da indústria se desenvolverá em torno disso.

Ser capaz de compreender o tipo de requisitos necessários dos diferentes fornecedores de chiplets e ser capaz de se comunicar através desses limites será muito importante. Ferramentas e metodologias de simulação serão importantes para trabalhar no que pensamos como fronteiras tradicionais. Então, sim, isso vai mudar a forma como projetamos os chips ou projetamos as partes empacotadas, e isso definitivamente mudará como o ecossistema semicondutor evolui com o tempo.

IEEE Spectrum: Você pode falar um pouco mais sobre esse ecossistema? Se você é uma startup fabless daqui a 10 anos, como é? Como a revolução do chiplet pode mudar o que essas empresas realmente tentam fazer?

Nagisetty: Eu acho que este é realmente um momento realmente empolgante para startups fabless, precisamente por causa da possibilidade de criar um subsistema IP menor que pode ser extremamente valioso quando é integrado usando uma abordagem chiplet.

Um dos objetivos do programa DARPA CHIPS é essencialmente apoiar a reutilização de propriedade intelectual e também reduzir o custo geral de engenharia não recorrente da produção de um produto. A abordagem chiplet permite que uma startup fabless foque na parte do IP que é extremamente boa, e não necessariamente se preocupa com o resto.

Eu penso na abordagem chiplet como um kickstart para startups fabless, e isso também faz parte de uma coisa maior que a DARPA está patrocinando, que é a ERI, ou a Iniciativa de Ressurgimento da Eletrônica, porque como o número de empresas que são capazes de suportar desenvolvimento de tecnologia de semicondutores de ponta caiu ao longo dos anos, a capacidade de pequenas empresas para inovar nesse mercado sofreu. Isso essencialmente abre caminho para muito mais inovação e, especificamente, de startups sem fabulação. Eu acho que isso vai ser uma plataforma para a inovação avançar, e isso será muito importante para a indústria. E é por isso que acho que é um momento super emocionante em termos da indústria de semicondutores, porque vamos ver muitas mudanças e muitas oportunidades se desenvolvendo com isso.

IEEE Spectrum: Com que rapidez os chiplets se desenvolverão até chegarmos ao ponto em que startups e empresas menores possam participar efetivamente?

Nagisetty: Então há algumas coisas que aconteceram recentemente. Há um novo fórum do setor chamado ODSA, que é o projeto Arquiteturas Específicas de Domínio Aberto . E está se tornando parte de uma colaboração em toda a indústria chamada de Projeto Open Compute. As empresas estão chegando às reuniões da ODSA e falando sobre seus interesses em usar a integração em nível de pacote e uma abordagem chiplet. Há também o recente anúncio do link compute express [CXL ], como uma interface coerente para aceleradores.

Parece que muitas coisas estão acontecendo rapidamente em apoio a esse novo tipo de ecossistema, baseado em aceleradores e baseado na integração de pacotes. Eu não posso realmente olhar em uma bola de cristal e dizer exatamente quanto tempo levará. Mas suspeito que não demorará tanto, talvez alguns anos. E, em alguns casos, estamos vendo os primeiros pontos de prova que já estão acontecendo.

IEEE Spectrum: Os chiplets precisarão de algum tipo de inteligência integrada no substrato ou no pacote, eventualmente?

Nagisetty: Bem, acho que vamos ver como isso evolui. Eu acho que é realmente uma decisão arquitetônica. Eu acho que há uma grande variedade de possibilidades aqui. E quando você fala sobre colocar inteligência no substrato, você pode ter um substrato que é inteligente empilhado em outro substrato que é puramente apenas uma interconexão. Portanto, haverá hierarquias e talvez até mesmo um tipo de substrato híbrido em que você tenha algum tipo de inteligência, mas talvez em um nó de tecnologia muito mais antigo que seja realmente otimizado para algo totalmente diferente.

IEEE Spectrum: Então, o que vem a seguir no desenvolvimento de tecnologia chiplet na Intel?

Nagisetty: Bem, o que posso dizer é que as coisas que já mostramos no mercado são os principais exemplos de como iremos criar virtualmente todos os nossos produtos no futuro. Temos muita pista com cada um desses esquemas de integração, e estamos apenas começando nessa direção. Mas com essas tecnologias no nosso plano de jogo, estamos realmente bem posicionados para avançar nas próximas gerações.

Etapas da Intel para integração heterogênea

https://www.eetimes.com/document.asp?doc_id=1334073

A Intel afirma que ter tecnologias de empacotamento 2D e 3D dá a flexibilidade de combinar pequenos pacotes de IP para atender às demandas de uma variedade de aplicações, envelopes de energia e fatores de forma. (Fonte: Intel)

https://www.eetimes.com/document.asp?doc_id=1334158&page_number=2

Intel revela 10 processos de 22 nm

https://www.eetimes.com/document.asp?doc_id=1331531&page_number=2#

Kanter elogiou o avanço do transistor COAG da Intel. No entanto, até que a empresa publique como ela fabrica dispositivos COAG, não será claro se ela pode usar o design como uma nova maneira de otimizar a resistência de contato e, assim, diferenciar seus processos.

Visão da Intel sobre a Revolução Chiplet

Ramune Nagisetty está ajudando a Intel a estabelecer seu lugar em um novo ecossistema da indústria centrado em chiplets

https://spectrum.ieee.org/tech-talk/semiconductors/processors/intels-view-of-the-chiplet-revolution

Chiplets são uma maneira de fazer sistemas que executam muito como se fossem todos um chip, apesar de serem compostos por vários chips menores. Eles são amplamente vistos como uma parte do plano da indústria de computação para manter os sistemas funcionando melhor e melhor, apesar do fato de que o tradicional escore Lei de Moore está chegando ao fim . Os defensores dizem que os benefícios incluirão sistemas mais especializados e maior rendimento, entre outras coisas. Mas o mais importante, eles podem levar a uma grande mudança na indústria de semicondutores, onde o produto final pode se tornar um pequeno e especializado chiplet destinado a ser combinado no mesmo pacote com um processador de uso geral e muitos outros chiplets especiais. Ramune NagisettyEngenheiro principal e diretor de integração de processos e produtos do grupo de desenvolvimento de tecnologia da Intel em Oregon, tem trabalhado para ajudar a desenvolver um ecossistema chiplet de toda a indústria. Ela disse ao IEEE Spectrum sobre isso e as tecnologias da Intel envolvidas em 21 de março de 2019.

Ramune Nagisetty em:

Quais são os chiplets?

chiplets são e diria por que eles estão se tornando importantes?

Ramune Nagisetty: Um chiplet é uma peça física de silício. Ele encapsula um subsistema IP (propriedade intelectual). E foi projetado para integrar-se a outros chiplets por meio da integração em nível de pacote, normalmente por meio da integração avançada de pacotes e do uso de interfaces padronizadas.

Por que eles estão se tornando importantes? É porque não existe uma abordagem única que funcione mais. Temos uma explosão nos diferentes tipos de computação e cargas de trabalho, portanto, há várias arquiteturas diferentes que estão surgindo para oferecer suporte a esses diferentes tipos de modelos de computação. Basicamente, a integração heterogênea da melhor tecnologia é uma maneira de continuar as tendências de desempenho da lei de Moore.

IEEE Spectrum: Quando você fala sobre tecnologias heterogêneas, você também quer dizer materiais semicondutores além do silício?

Nagisetty: Eu diria que não é necessariamente apenas silício, haverá outros tipos de tecnologias semicondutoras também. Você pode incluir coisas como tecnologias baseadas em germânio ou III-Vs. No futuro, teremos tipos mais variados de tecnologias de semicondutores. Hoje, é principalmente silício.

Mesmo com apenas chiplets baseados em silício, eles certamente estarão em diferentes nós de tecnologia. Eles geralmente são ajustados para melhor desempenho em diferentes áreas - seja digital, analógica, RF ou, por exemplo, tecnologias de memória.

A memória de alta largura de banda, ou HBM, é essencialmente um dos primeiros pontos de prova da integração em pacotes de silício heterogêneo. A memória é essencialmente o primeiro tipo de integração heterogênea que está realmente ganhando força usando a embalagem avançada.

IEEE Spectrum: A maneira da Intel conectar os chiplets é chamada de ponte integrada de interconexão de vários terminais . Por favor, diga-nos o que é e como funciona.

Nagisetty: Você pode pensar nisso como uma ponte de alta densidade conectando dois chiplets juntos, que é essencialmente a melhor maneira de descrevê-lo. Eu acho que muitas pessoas estão familiarizadas com a idéia de usar um interposer de silício como um substrato de embalagem avançado. [Os interposers de silício são substratos de silício com interconexões densas e vias de silício integradas nelas. Eles permitem conexões de alta largura de banda entre os chips.]

Imagem: Intel

Um EMIB [círculo] conecta-se a chips dentro do mesmo pacote usando interconexões de alta densidade. Os solavancos de conexão que ligam os chips ao EMIB têm um pitch muito mais fino do que os solavancos normais [bottom left].

O que é um EMIB é, essencialmente, um pedaço muito pequeno de um interposer de silício que possui interconexões de densidade muito alta e o que chamamos de microbumps em uma densidade muito maior do que você encontraria em um substrato de embalagem padrão. [Microbombas são pequenas bolas de solda que ligam um chip a outro chip ou a interconexões de alta densidade de um pacote.]

Esse EMIB ou bridge é essencialmente incorporado em um substrato de embalagem padrão. Com o EMIB, você é essencialmente capaz de obter a maior densidade de interconexão exatamente onde precisa e, em seguida, pode usar um substrato de embalagem padrão para o restante da interconexão.

Há muitos benefícios em fazer isso dessa maneira. Um deles é custado porque o custo de um interposer de silício é proporcional à área desse interposer. Então, neste caso, localizamos realmente a interconexão de alta densidade na área onde é necessária. E também há benefícios em termos de perda geral de inserção - a atenuação do sinal devido às propriedades do material - usando um substrato de embalagem padrão em vez de um intermediário de silício.

IEEE Spectrum: O que a Intel usou o EMIB até agora?

Nagisetty: A Intel na verdade tem várias soluções chiplet demonstradas, e eu gostaria de falar sobre cada uma delas, porque acho que ajuda a esclarecer o que eu acho que são as três direções diferentes que os chiplets seguirão.

A Intel tem duas soluções baseadas no EMIB atualmente, mas são muito diferentes. O primeiro é o Kaby Lake-G , e é basicamente onde integramos uma GPU AMD Radeon e uma memória de alta largura de banda [HBM] com nosso chip de CPU. Usamos o EMIB para integrar a GPU e a HBM, usando uma interface da HBM dentro do pacote. E então usamos PCI Express , que é uma interface padrão de placa de circuito, dentro do pacote para integrar a GPU e a CPU.

O que é realmente interessante sobre essa solução é que estamos usando silício desenvolvido externamente a partir de várias fundições e estamos usando interfaces padrão da indústria comuns - HBM e PCI Express - para criar um produto de primeira classe. Nesse caso, pegamos um componente (GPU com HBM) que era capaz de ficar sozinho em uma placa e o integramos em um pacote. O PCI Express foi projetado para enviar sinais por longas distâncias mais típicas de uma placa. Quando você coloca dentro de um pacote, na verdade não é necessariamente uma solução ideal, mas é uma solução rápida porque estamos utilizando interfaces que já existem na indústria.

IEEE Spectrum: Qual a vantagem desta integração?

Nagisetty: Neste caso, o que ganhamos é um enorme fator de forma, ou tamanho, melhoria. Para jogos móveis, caber dentro de um design de laptop é realmente importante. Essencialmente, você está sempre negociando fator de forma, poder e desempenho um do outro. Portanto, neste caso, ele é realmente otimizado para ter uma solução de primeira classe no menor tamanho possível.

IEEE Spectrum: Qual é o outro exemplo chiplet que você queria descrever?

Nagisetty: A próxima coisa que eu gostaria de falar é sobre o FPGA Stratix 10, que na verdade foi a primeira demonstração da solução EMIB da Intel. O Stratix 10 tem um FPGA da Intel no centro dele. E então tem seis chiplets em torno do FPGA. Quatro deles são chiplets transceptores de alta velocidade, e dois deles são chiplets de memória de alta largura de banda, e todos eles são montados em um pacote. Este exemplo integra seis diferentes nós de tecnologia de três fundições diferentes; então é mais uma prova de interoperabilidade em termos de diferentes fundições.

Imagem: Intel

A Intel Stratix 10 é um excelente exemplo do uso de EMIBs para conectar chiplets em um pacote.

A segunda coisa é que ele usa uma interface die-to-die padrão da indústria chamada AIB, que é o Advanced Interface Bus da Intel. Ele foi criado para este produto e é essencialmente a semente de um padrão de mercado para uma interconexão de lógica para lógica de alta largura de banda dentro do pacote. Portanto, o HBM é o primeiro padrão para integração de memória e o AIB é o primeiro padrão para integração lógica.

O AIB é uma interface que pode ser usada com a solução EMIB da Intel e com soluções concorrentes, como interpositores de silício. Mas o que é realmente bom nessa interface e o FPGA no centro desse ecossistema é a abordagem de combinação e combinação que é possível. Há muitas empresas diferentes e muitas universidades diferentes que estão criando chiplets usando o AIB por meio de um esforço patrocinado pelo programa CHIPS ( Integração Heterogênea Comum e Reutilização de Estratégias de IP ) da DARPA .

Foveros , da Intel , que é o nosso empilhamento de lógico de lógica lógica, e que foi falado pela primeira vez em dezembro e depois o produto, chamado Lakefield, foi anunciado em janeiro na CES . Esta é a integração do chiplet, mas em vez do empilhamento horizontal, é o empilhamento vertical.

Esse tipo de integração permite que você obtenha uma largura de banda extremamente alta entre os dois chiplets. Mas ele é baseado em interfaces proprietárias internas e os dois morrem são essencialmente co-projetados porque precisam ser planejados juntos para gerenciar coisas como distribuição de energia e térmicas.

Para o empilhamento lógico de matrizes lógicas, provavelmente será um prazo muito maior antes de vermos os padrões emergentes na área da indústria, porque os moldes são essencialmente co-projetados juntos. O empilhamento de memória no topo da lógica provavelmente será o primeiro lugar onde qualquer tipo de padrão se desenvolve para o empilhamento tridimensional.

/ P1274 é o nome da Intel para o seu processo de 10nm de alto desempenho. P1222 é o seu processo 22FFL (22nm, FinFET, Low Power), que é otimizado para vazamento de corrente muito menor. Assim como a conexão Foveros entre os módulos de computação e de E / S, o produto usará a memória empacotada convencional em pacote-em-pacote.

O smicrobumps da Enlarge / Foveros permitem comunicação cara a cara entre os dados.

Diagrama de vista lateral da tecnologia de empacotamento Foveros 3D da Intel. (Fonte: Intel)

IEEE Spectrum: Ao projetar para chips empilhados, quais são algumas das coisas que você deve observar?

Nagisetty: Problemas térmicos são os principais. Como você pode imaginar, o empilhamento de folhas exacerba qualquer tipo de problema térmico. Então, precisamos fazer um planejamento cuidadoso do piso para acomodar os pontos de acesso térmicos. Também precisamos considerar a arquitetura de todo o sistema. As implicações do uso do empilhamento 3D levarão até as decisões arquiteturais, não apenas a arquitetura física, mas toda a CPU ou GPU e a arquitetura do sistema.

IEEE Spectrum: Que tipos de padrões ainda são necessários para avançar os chiplets?

Nagisetty: Os padrões do setor em relação aos testes são realmente importantes. Normalmente, fazemos testes com peças totalmente empacotadas. Precisamos ser capazes de colocar “bons dados conhecidos” (chiplets que sabemos que funcionam) dentro de um pacote, para que não acabemos inadvertidamente com a queda do rendimento devido a um único chiplet ser ruim e os outros chiplets serem bons. Então, precisamos de uma estratégia para bons dados conhecidos e precisamos de uma estratégia para teste.

Outra coisa que precisamos é de suporte a vários fornecedores para gerenciamento de energia e térmica. Isso significa ser capaz de ter ganchos em todos os chiplets integrados para gerenciar energia e gerenciar térmicas.

E, em termos de intraoperabilidade elétrica, a AIB - a interface que lançamos em julho passado - é realmente apenas um padrão no que chamamos de nível PHY, que é a interface física e elétrica. Mas precisamos ter padrões que também percorram os protocolos da camada superior.

Eu acho que o último, e pode parecer óbvio, é um padrão mecânico - literalmente a colocação de microbombas e roteamento entre padrões de necessidades de microbombas para suportar a interoperabilidade.

Foto: Intel

Ramune Nagisetty

IEEE Spectrum: Você pode nos contar um pouco mais sobre o problema do “conhecido bom die” e como os testes terão que ser diferentes com os chiplets?

Nagisetty: Bem, é realmente muito diferente, porque a capacidade de garantir completamente o Known Good Die é geralmente baseada em testes a quente de uma parte empacotada. Portanto, com os chiplets agora você tem que ser capaz de testar essencialmente os chips mortos antes de serem empacotados - no mesmo nível de capacidade. É mais fácil testar peças empacotadas, facilitar a entrega de energia e assim por diante. Quando você faz isso com o dado desencapado, você tem desafios com sondagem, porque você tem os pads extras que você precisa para configurar as sondas.

A outra coisa é que qualquer coisa que você precise para testar se ela morrer independentemente, seja um relógio ou qualquer outro tipo de garantia para poder testar completamente cada chiplet, precisa ser projetada no chiplet. Os chiplets não podem ser co-dependentes uns dos outros para testá-los. Eles precisam ser totalmente testados individualmente antes de serem empacotados.

Há trabalho acontecendo nesta área. E é extremamente importante porque, você pode imaginar, no momento em que você tem uma parte embalada com muitos chiplets dentro dele, há muito valor nessa parte empacotada. E se qualquer um desses chiplets for ruim e não for redundante ou consertável, então você essencialmente descartou muitos outros chiplets que têm valor.

IEEE Spectrum: Não é um dos benefícios propostos de chiplets que eles levam a um melhor rendimento, porque eles são fisicamente menores e, portanto, menos propensos a erros?

IEEE Spectrum: Como o chiplets mudará a maneira como as coisas são projetadas?

Nagisetty: A integração de memória de alta largura de banda é realmente o primeiro ponto de prova, e já está sendo amplamente usada em GPUs e também com processadores AI em sistemas de alto desempenho. Portanto, neste caso, as chiplets e a integração de pacotes de memória já estão mudando a maneira como os chips são projetados e integrados.

Co-design de chiplets certamente será uma área importante que se desenvolverá. O que eu realmente acho que vai acontecer é que teremos vários fornecedores fornecendo chiplets. E então, quais são os limites arquitetônicos? E como projetamos os melhores produtos baseados nos blocos de construção que temos? Nós estamos realmente apenas no começo do que eu acho que é uma revolução. Um novo ecossistema da indústria se desenvolverá em torno disso.

Ser capaz de compreender o tipo de requisitos necessários dos diferentes fornecedores de chiplets e ser capaz de se comunicar através desses limites será muito importante. Ferramentas e metodologias de simulação serão importantes para trabalhar no que pensamos como fronteiras tradicionais. Então, sim, isso vai mudar a forma como projetamos os chips ou projetamos as partes empacotadas, e isso definitivamente mudará como o ecossistema semicondutor evolui com o tempo.

IEEE Spectrum: Você pode falar um pouco mais sobre esse ecossistema? Se você é uma startup fabless daqui a 10 anos, como é? Como a revolução do chiplet pode mudar o que essas empresas realmente tentam fazer?

Nagisetty: Eu acho que este é realmente um momento realmente empolgante para startups fabless, precisamente por causa da possibilidade de criar um subsistema IP menor que pode ser extremamente valioso quando é integrado usando uma abordagem chiplet.

Um dos objetivos do programa DARPA CHIPS é essencialmente apoiar a reutilização de propriedade intelectual e também reduzir o custo geral de engenharia não recorrente da produção de um produto. A abordagem chiplet permite que uma startup fabless foque na parte do IP que é extremamente boa, e não necessariamente se preocupa com o resto.

Eu penso na abordagem chiplet como um kickstart para startups fabless, e isso também faz parte de uma coisa maior que a DARPA está patrocinando, que é a ERI, ou a Iniciativa de Ressurgimento da Eletrônica, porque como o número de empresas que são capazes de suportar desenvolvimento de tecnologia de semicondutores de ponta caiu ao longo dos anos, a capacidade de pequenas empresas para inovar nesse mercado sofreu. Isso essencialmente abre caminho para muito mais inovação e, especificamente, de startups sem fabulação. Eu acho que isso vai ser uma plataforma para a inovação avançar, e isso será muito importante para a indústria. E é por isso que acho que é um momento super emocionante em termos da indústria de semicondutores, porque vamos ver muitas mudanças e muitas oportunidades se desenvolvendo com isso.

IEEE Spectrum: Com que rapidez os chiplets se desenvolverão até chegarmos ao ponto em que startups e empresas menores possam participar efetivamente?

Nagisetty: Então há algumas coisas que aconteceram recentemente. Há um novo fórum do setor chamado ODSA, que é o projeto Arquiteturas Específicas de Domínio Aberto . E está se tornando parte de uma colaboração em toda a indústria chamada de Projeto Open Compute. As empresas estão chegando às reuniões da ODSA e falando sobre seus interesses em usar a integração em nível de pacote e uma abordagem chiplet. Há também o recente anúncio do link compute express [CXL ], como uma interface coerente para aceleradores.

Parece que muitas coisas estão acontecendo rapidamente em apoio a esse novo tipo de ecossistema, baseado em aceleradores e baseado na integração de pacotes. Eu não posso realmente olhar em uma bola de cristal e dizer exatamente quanto tempo levará. Mas suspeito que não demorará tanto, talvez alguns anos. E, em alguns casos, estamos vendo os primeiros pontos de prova que já estão acontecendo.

IEEE Spectrum: Os chiplets precisarão de algum tipo de inteligência integrada no substrato ou no pacote, eventualmente?

Nagisetty: Bem, acho que vamos ver como isso evolui. Eu acho que é realmente uma decisão arquitetônica. Eu acho que há uma grande variedade de possibilidades aqui. E quando você fala sobre colocar inteligência no substrato, você pode ter um substrato que é inteligente empilhado em outro substrato que é puramente apenas uma interconexão. Portanto, haverá hierarquias e talvez até mesmo um tipo de substrato híbrido em que você tenha algum tipo de inteligência, mas talvez em um nó de tecnologia muito mais antigo que seja realmente otimizado para algo totalmente diferente.

IEEE Spectrum: Então, o que vem a seguir no desenvolvimento de tecnologia chiplet na Intel?

Nagisetty: Bem, o que posso dizer é que as coisas que já mostramos no mercado são os principais exemplos de como iremos criar virtualmente todos os nossos produtos no futuro. Temos muita pista com cada um desses esquemas de integração, e estamos apenas começando nessa direção. Mas com essas tecnologias no nosso plano de jogo, estamos realmente bem posicionados para avançar nas próximas gerações.

Etapas da Intel para integração heterogênea

https://www.eetimes.com/document.asp?doc_id=1334073

A Intel afirma que ter tecnologias de empacotamento 2D e 3D dá a flexibilidade de combinar pequenos pacotes de IP para atender às demandas de uma variedade de aplicações, envelopes de energia e fatores de forma. (Fonte: Intel)

O que uma concorrência que coça o cangote não faz, hein?!

EDIT:

10ª geração e ainda PCIe 3.0?

PCIe 4.0 só na 20ª gen?

Se ao menos ela fosse real xDTava vendo essa imagem:

Socket novo pros mesmos 14nm+++? É isso mesmo?

Origem REAL dessa imagem: De um -chan da vida, mais especificamente o 5chan:

https://egg.5ch.net/test/read.cgi/jisaku/1562485578/628

Detalhes que implicam na falsidade: Qualidade da imagem, excesso de detalhes (coisa que a Intel não faz), erros nas informações (cache, fora da formatação padrão da Intel)

Para complementar isso com informação CORRETA, o novo socket será o LGA-1200, com chipset 400-series (H410, B460, H470, Z490), e o TDP virá nas configurações de 35W, 65W, 80W, 95W e 125W. Das informações REAIS que estão circulando posso dizer que não existirá processadores com HT e, por mais estranho que possa parecer, nenhum CPU com denominação K, significando que ou todos eles irão fazer OC, ou nenhum deles fará. Como a Intel lançou um programa de OC automático, é mais fácil ser a primeira alternativa OU nenhum modelo K foi vazado até agora.

PCI-Express 4.0 apenas a partir dos Tigerlake para mobile e Icelake nos servidores. No desktop não há nenhuma menção, então pode vir com os Alderlake ou Meteorlake em 2022.10ª geração e ainda PCIe 3.0?

PCIe 4.0 só na 20ª gen?

Essa ainda esse ano. Em 2021 deve sair os processadores de 10nm.Mesmo que essa imagem fosse verdade, essa linha sairia quando? 2021 com sorte?

Mesmo que essa imagem fosse verdade, essa linha sairia quando? 2021 com sorte?

Todas as indicações (confiáveis) que vimos até hoje sugerem que os processadores Comet Lake não serão lançados antes de 2020. É este, no entanto, o kit de desenvolvimento formal de software (estando pronto agora), então pode sugerir que existe uma possibilidade realística antes do final do ano.

https://www.eteknix.com/intel-10-core-comet-lake-cpus-may-arrive-sooner-than-expected/

Essa ainda esse ano. Em 2021 deve sair os processadores de 10nm.

No cronograma oficial da INTEL, os 14nm irão até 2021.

Então 10nm para Desktop somente a partir de 2022 em diante.

Nops, esse ano sai o 9900KS, a décima geração para desktop sai início do ano que vem.Essa ainda esse ano. Em 2021 deve sair os processadores de 10nm.

Na verdade na verdade, lança final desse ano como paper-launch, mas para as lojas só em 2020.

Final de 2020 sai a 11ªgen, os RocketLake. Aqui tenho informações conflitantes: Algumas fontes dizem que os RocketLake-S serão die-expand (oposto do die-shrink) do WillowCove, ou seja, uma uArch pensada em 10nm++ mas fabricada/portada para 14nm+++; Outras dizem que será mais um refresh dos Skylake em 14nm.

Depois, no final de 2021, vem a 12ªgen que se chamará AlderLake. Essa uArch pode ser em 14nm como die-expand da GoldenCove ou ser direto em 10nm, mas o estado atual dos 10nm faz-me acreditar na primeira possibilidade. Somente em 2022 (Q4) que veremos os Meteorlake, uArch em 7nm com núcleos OceanCove, ou seja, a Intel tem planos para pular completamente os 10nm no desktop caso o mesmo não atinja altas frequências (que é o marketing dela no desktop).

Nops, esse ano sai o 9900KS, a décima geração apra desktop sai início do ano que vem.

Na verdade na verdade, lança final desse ano como paper-launch, mas para as lojas só em 2020.

Final de 2020 sai a 11ªgen, os RocketLake. Ai começam as informações conflitantes: Algumas fontes dizem que os RocketLake-S serão die-expand (oposto do die-shrink) do WillowCove, ou seja, uma uArch pensada em 10nm++ mas fabricada/portada para 14nm+++; Outras dizem que será mais um refresh dos Skylake em 14nm.

Depois, no final de 2021, vem a 12ªgen que se chamará AlderLake. Essa uArch pode ser em 14nm como die-expand da GoldenCove ou ser direto em 10nm, mas o estado atual dos 10nm faz-me acreditar na primeira possibilidade. Somente em 2022 (Q4) que veremos os Meteorlake, uArch em 7nm com núcleos OceanCove, ou seja, a Intel pulará os 10nm completamente no desktop.

Como a Intel irá lançar os 7nm para desktop em 2022 com apenas duas fábricas ? E ainda precisa atender a demanda dos segmento corporativo e notebook.

Rapaz, são as informações que tenho, e como qualquer roadmap de longas datas podem ocorrer mudanças no meio do caminho (o que é comum com a Intel, vide os 10nm para 2014).Como a Intel irá lançar os 7nm para desktop em 2022 com apenas duas fábricas ? E ainda precisa atender a demanda dos segmento corporativo e notebook.

O que sei é que em 2021 sai uma GPU em 7nm para DC (ArcticSounds) e expande-se o maquinário. Em 2022 sai a família Meteorlake para notebooks em 7nm+ e, em paper-launch, os Meteorlake 7nm para desktop, logo mesmo sendo 2022 na verdade é 2023.

Essas informações coincidem com os dois roadmaps vazados pelo site Tweakers e com o próprio roadmap de escalas da Intel. Como/se ela conseguirá cumprir isso, ai já não é comigo, é com os engenheiros dela xD

Última edição:

Rapaz, são as informações que tenho, e como qualquer roadmap de longas datas podem ocorrer mudanças no meio do caminho (o que é comum com a Intel, vide os 10nm para 2014).

O que sei é que em 2021 sai uma GPU em 7nm para DC (JupiterSounds) e expande-se o maquinário. Em 2022 sai a família Meteorlake para notebooks em 7nm+ e, em paper-launch, os Meteorlake 7nm para desktop, logo mesmo sendo 2022 na verdade é 2023.

Essas informações coincidem com os dois roadmaps vazados pelo site Tweakers e com o próprio roadmap de escalas da Intel. Como/se ela conseguirá cumprir isso, ai já não é comigo, é com os engenheiros dela xD

INTEL GPU (placa de vídeo) de 7nm chegam quando para DESKTOP ?

Última edição:

Até onde sei, final de 2020 em 10nm++ (ArcticSounds). Final de 2021 é que virão as GPUs também em 7nm. Agora se a Intel conseguirá cumprir isso, acho difícil, é muita coisa em 7nm para quem tem quase nenhuma fábrica nessa escala.INTEL GPU (placa de vídeo) de 7nm chegam quando para DESKTOP ?

Eu não to satisfeito com os ganhos da terceira geração ryzen e gostei das quedas de preço mas as falhas de segurança da intel tornam inaceitável pagar caro numa plataforma morta.Se chegar com os preços que o amigo postou, acho que muita gente vai abandonar os ryzen

Eu vou continuar com ryzen até a intel aposentar o skylake. O pior é vir plataforma nova com ddr4 ainda. Vai durar só 2 anos ai toca trocar de novo quando vier o refresh do ice lake com ddr5 em 2021. Bom, am4 morre em 2020. Seguro até 2021e na época do ddr5 talvez seja a hora de voltar pra intel. Por enquanto nem se fosse mais barato.

Eu não to satisfeito com os ganhos da terceira geração ryzen e gostei das quedas de preço mas as falhas de segurança da intel tornam inaceitável pagar caro numa plataforma morta.

Eu vou continuar com ryzen até a intel aposentar o skylake. O pior é vir plataforma nova com ddr4 ainda. Vai durar só 2 anos ai toca trocar de novo quando vier o refresh do ice lake com ddr5 em 2021. Bom, am4 morre em 2020. Seguro até 2021e na época do ddr5 talvez seja a hora de voltar pra intel. Por enquanto nem se fosse mais barato.

Se vc for trocar de combo mobo mais CPU em 2021 não seria o mesmo de ter comprado intel em uma plataforma "morta"? Sei lá é bem legal poder trocar de processador sem trocar de mobo, principalmente pra quem compra primeiro um processador mais básico e depois faz um upgrade. Mas pra quem já compra um processador mais high end vejo pouco uso de maneira geral.

Eu costumo ficar com um processador pelo menos 3 anos a não ser que tenham ganhos muito grandes de performance de uma geração para outra o que não costuma acontecer neste ramo. Também penso em trocar quando tiver processadores DDR5 e quando isto acontecer tanto a intel quanto a AMD precisarão de um novo socket/chipset. Quem tem um 8700 ou 8700k ou similar AMD não vejo motivo algum para trocar de processador no curto prazo.

Última edição:

Eu não to satisfeito com os ganhos da terceira geração ryzen e gostei das quedas de preço mas as falhas de segurança da intel tornam inaceitável pagar caro numa plataforma morta.

Eu vou continuar com ryzen até a intel aposentar o skylake. O pior é vir plataforma nova com ddr4 ainda. Vai durar só 2 anos ai toca trocar de novo quando vier o refresh do ice lake com ddr5 em 2021. Bom, am4 morre em 2020. Seguro até 2021e na época do ddr5 talvez seja a hora de voltar pra intel. Por enquanto nem se fosse mais barato.

eu também não fiquei satisfeito com o ryzen 3, vejo a galera comemorando que os 3600 e 3700x ganha em alguns jogos do 8700k e outros game perdem, mas o processador custa 1200 reais e tem a performance similar a um processador de 2017Se vc for trocar de combo mobo mais CPU em 2021 não seria o mesmo de ter comprado intel em uma plataforma "morta"? Sei lá é bem legal poder trocar de processador sem trocar de mobo, principalmente pra quem compra primeiro um processador mais básico e depois faz um upgrade. Mas pra quem já compra um processador mais high end vejo pouco uso de maneira geral.

Eu costumo ficar com um processador pelo menos 3 anos a não ser que tenham ganhos muito grandes de performance de uma geração para outra o que não costuma acontecer neste ramo. Também penso em trocar quando tiver processadores DDR5 e quando isto acontecer tanto a intel quanto a AMD precisarão de um novo socket/chipset. Quem tem um 8700 ou 8700k ou similar AMD não vejo motivo algum para trocar de processador no curto prazo.

, EU esperava o 3800 no mesmo nível do 9900k em jogos.

, EU esperava o 3800 no mesmo nível do 9900k em jogos.só fiz a comparação em jogos, pois esse é meu único uso do PC

a questão de Socket, não ligo que intel muda isso todo ano, pois eu fico mais de 5 anos com o mesmo processador e a galera do 8700k que comprou em 2017 e começo de 2018, deve está feliz, processador na época custava 1500 reais

Users who are viewing this thread

Total: 3 (membros: 0, visitantes: 3)