De acordo com fontes internas ele queria mais tempo com a família.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

[TÓPICO DEDICADO] INTEL Comet / Rocket / Alder / Raptor Lake

- Iniciador de Tópicos brender

- Data de Início

cara que saiu por treta internas e vao dar uma grana pra manter boca fechada por um tempo(deve ter cláusula de contrato, mas deve ter ganhado um "bonus" pra n soltar os motivos reais da saída)

Analista tem opinião negativa sobre Keller deixando a Intel

Na última vez em que alguém saiu por "razões pessoais" na Intel, ele teve um caso interno ... ele não conseguia fazer com que seus 10 nm de hardware funcionassem.

Intel diz que designer de chips renuncia por motivos pessoais

finance.yahoo.com

finance.yahoo.com

A Intel Corp. disse que o principal designer de chips, Jim Keller, renunciou por motivos pessoais, causando um duro golpe à maior fabricante de semicondutores do mundo, enquanto tenta reafirmar sua liderança no setor.

A renúncia de Keller é efetiva imediatamente, mas ele atuará como consultor da empresa por seis meses, disse a Intel em comunicado.

Keller foi vice-presidente sênior e gerente geral de engenharia de silício. O ex-executivo da Apple Inc., Tesla Inc. e Advanced Micro Devices Inc. é creditado com os principais programas que produziram alguns dos componentes mais importantes da história do setor. Enquanto a Intel continua a registrar vendas recordes, seus rivais afirmam que seus produtos são agora com desempenho igual ou melhor e que os atrasos na fabricação da Intel a tornam mais vulnerável à concorrência do que há anos. Ao mesmo tempo, clientes como a Amazon.com Inc. estão cada vez mais projetando seus próprios processadores.

"A saída de Keller é importante e sugere que tudo o que ele estava implementando na Intel não estava funcionando ou o antigo guarda da Intel não queria implementá-la", escreveu Hans Mosesmann, analista da Rosenblatt Securities, em nota aos investidores. “A solução para essa situação é que os roteiros dos processadores e dos nós dos processos da Intel estarão mais em fluxo ou interrompidos do que esperávamos.”

A Intel disse que seu grupo de tecnologia, liderado por Murthy Renduchintala, diretor de engenharia da empresa, promoveu quatro engenheiros para cargos mais altos.

Keller era um executivo sênior da PA Semi, que mais tarde foi adquirida pela Apple para aumentar seus esforços de componentes internos. Ele projetou alguns dos primeiros chips internos para iPhone e iPad da Apple, que são os principais componentes personalizados em seus dispositivos mais vendidos.

Fato curioso

Na última vez em que alguém saiu por "razões pessoais" na Intel, ele teve um caso interno ... ele não conseguia fazer com que seus 10 nm de hardware funcionassem.

Intel diz que designer de chips renuncia por motivos pessoais

Intel Says Top Chip Designer Resigns for Personal Reasons

(Bloomberg) -- Intel Corp. said top chip designer Jim Keller has resigned for personal reasons, dealing a blow to the world’s biggest semiconductor maker as it tries to reassert its industry leadership.Keller’s resignation is effective immediately but he will act as a consultant for the company...

A Intel Corp. disse que o principal designer de chips, Jim Keller, renunciou por motivos pessoais, causando um duro golpe à maior fabricante de semicondutores do mundo, enquanto tenta reafirmar sua liderança no setor.

A renúncia de Keller é efetiva imediatamente, mas ele atuará como consultor da empresa por seis meses, disse a Intel em comunicado.

Keller foi vice-presidente sênior e gerente geral de engenharia de silício. O ex-executivo da Apple Inc., Tesla Inc. e Advanced Micro Devices Inc. é creditado com os principais programas que produziram alguns dos componentes mais importantes da história do setor. Enquanto a Intel continua a registrar vendas recordes, seus rivais afirmam que seus produtos são agora com desempenho igual ou melhor e que os atrasos na fabricação da Intel a tornam mais vulnerável à concorrência do que há anos. Ao mesmo tempo, clientes como a Amazon.com Inc. estão cada vez mais projetando seus próprios processadores.

"A saída de Keller é importante e sugere que tudo o que ele estava implementando na Intel não estava funcionando ou o antigo guarda da Intel não queria implementá-la", escreveu Hans Mosesmann, analista da Rosenblatt Securities, em nota aos investidores. “A solução para essa situação é que os roteiros dos processadores e dos nós dos processos da Intel estarão mais em fluxo ou interrompidos do que esperávamos.”

A Intel disse que seu grupo de tecnologia, liderado por Murthy Renduchintala, diretor de engenharia da empresa, promoveu quatro engenheiros para cargos mais altos.

Keller era um executivo sênior da PA Semi, que mais tarde foi adquirida pela Apple para aumentar seus esforços de componentes internos. Ele projetou alguns dos primeiros chips internos para iPhone e iPad da Apple, que são os principais componentes personalizados em seus dispositivos mais vendidos.

--- Post duplo é unido automaticamente: ---

Fato curioso

Última edição:

Boatos apontam q falaram pra ele q vai ter 14nm++++++++ ele surtou e quebrou o proprio escritóriocara que saiu por treta internas e vao dar uma grana pra manter boca fechada por um tempo(deve ter cláusula de contrato, mas deve ter ganhado um "bonus" pra n soltar os motivos reais da saída)

Aos manjadores de INTEL

Quanto valeria o meu kit atual ?

Nunca fiz overclock por N motivos

4 anos de uso

Processador: i5 6600k Skylake |

Cooler: Cooler Master Hyper 212x |

www.coolermaster.com

www.coolermaster.com

Placa mãe: ASRock Fatal1ty Z170 Gaming K6

www.asrock.com

www.asrock.com

Quanto valeria o meu kit atual ?

Nunca fiz overclock por N motivos

4 anos de uso

Processador: i5 6600k Skylake |

Cooler: Cooler Master Hyper 212x |

Hyper 212X

The CoolerMaster Hyper 212X introduces several new features to the incredibly popular 212 series. It uses the same Patented Quad CDC Heatpipe array but features a completely new cooling fan and an improved fin-blade layout. Thanks to the new Smart Engine and 4th Generation Bearing, the MTBF has...

Placa mãe: ASRock Fatal1ty Z170 Gaming K6

ASRock > Fatal1ty Z170 Gaming K6

ASRock Super Alloy; Gaming Armor - CPU Power / Memory / VGA Card / Cooling / Internet / Audio; Supports 7th and 6th Generation Intel Core™ Processors (Socket 1151)<div class=Remark><span style=color:red;>*</span>8th Gen Intel Core™ desktop processors are supported with Intel 300 Series chipset...

Bacana, qual a placa mãe recomendada pra ele?

Pra quem vai só jogar, ele parece ser uma opção mais interessante que o R5 3600.

Última edição:

problema é ter que pegar uma z490 pra elevar o clock da memoria pra que ele entregue pouca coisa mais em games que o ryzen , fora que da pra colocar as novas levas dos 3600 a 4.4 , até 4.5 nas melhores samples , não vejo esses cpus vantajosas .Bacana, qual a placa mãe recomendada pra ele?

Pra quem vai só jogar, ele parece ser uma opção mais interessante que o R5 3600.

acho que quem consegue usar o Ryzen5 3600 pra trabalho, consegue fazer o com esse i5 tbBacana, qual a placa mãe recomendada pra ele?

Pra quem vai só jogar, ele parece ser uma opção mais interessante que o R5 3600.

Definitivamente.acho que quem consegue usar o Ryzen5 3600 pra trabalho, consegue fazer o com esse i5 tb

A diferença de desempenho, segundo o TechPowerUp, fica na casa dos 5% pra cima ou pra baixo em cima do 3600, dependendo se você joga ou usa pra desenvolvimento.

Fica pra cada um escolher qual critério alternativo usar (custo, valor de revenda, possibilidade de upgrade, garantia, etc.), pois em performance os dois são praticamente iguais.

Pra jogar a 144fps a AMD não tem uma resposta ao i5 10600K por enquanto.

se a intel liberasse OC em ram nas B460, ficaria bem interessante essa 10th, porém sem fazer isso fica complicado. Se não liberar OC em ram nas placas mid, acho que só 2 opções ficariam viáveis: casar um 10400f com uma H410 para CxB, ou uma Z490 + 10600k para desempenho max em jogos, se for para montar um octacore pra cima já seria mais vantagem ir de AMD mesmo.

Definitivamente.

A diferença de desempenho, segundo o TechPowerUp, fica na casa dos 5% pra cima ou pra baixo em cima do 3600, dependendo se você joga ou usa pra desenvolvimento.

Fica pra cada um escolher qual critério alternativo usar (custo, valor de revenda, possibilidade de upgrade, garantia, etc.), pois em performance os dois são praticamente iguais.

Pra jogar a 144fps a AMD não tem uma resposta ao i5 10600K por enquanto.

O 3600 empurra tranquilo acima dos 144 fps, inclusive no rainbow six pega mais de 250. Agora se quiser 250 fps no PUBG e 600 fps no CS, só intel mesmo, mas aí é pra profissional de e-sports, quem ganha dinheiro jogando.

Eu tenho um Zen 2 e ele não empurra 144 fps no Dota 2 sem quedas nem com tudo no mínimo.O 3600 empurra tranquilo acima dos 144 fps, inclusive no rainbow six pega mais de 250. Agora se quiser 250 fps no PUBG e 600 fps no CS, só intel mesmo, mas aí é pra profissional de e-sports ou quem ganha dinheiro jogando

O FPS médio fica bem alto (perto dos 300) mas as quedas ocorrem justamente nas horas mais importantes do jogo (team fights).

Intel usará transistores Nanowire / Nanoribbon em volume 'em cinco anos'

www.anandtech.com

www.anandtech.com

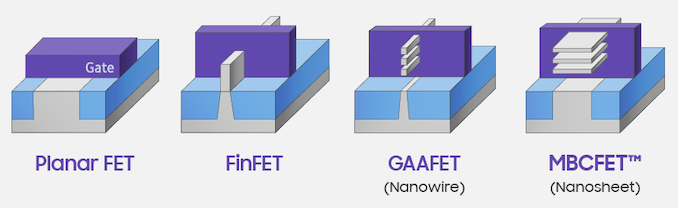

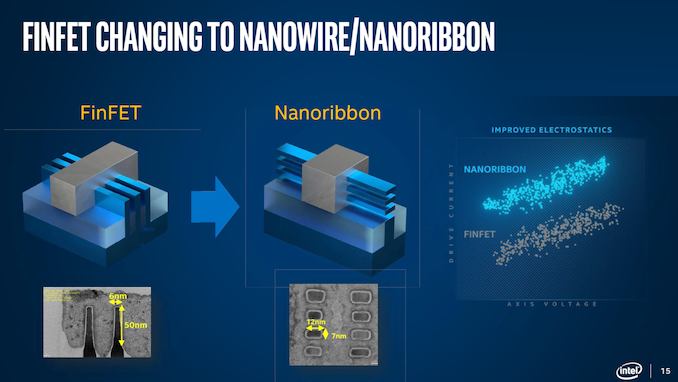

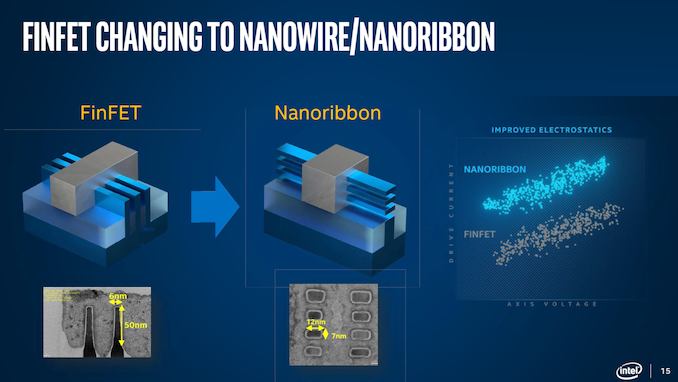

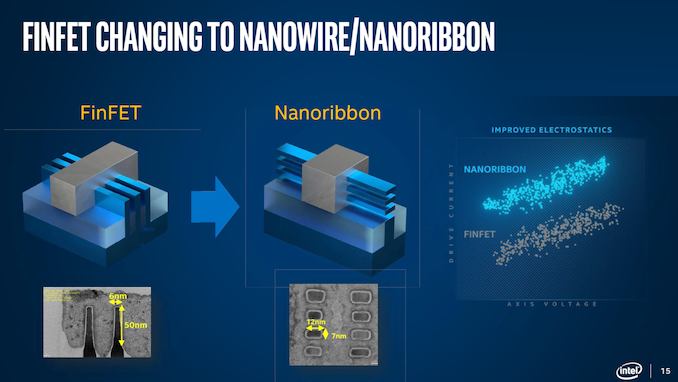

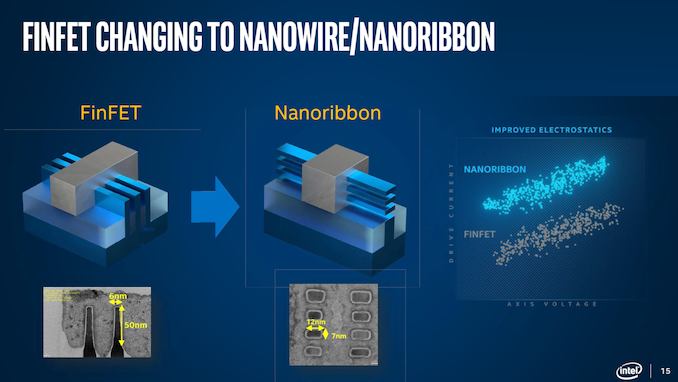

Este ano, na conferência internacional do VLSI, o CTO da Intel, Mike Mayberry, fez uma das apresentações plenárias, que este ano foi intitulada 'O Futuro da Computação'. Dentro da apresentação, várias novas tecnologias de fabricação foram discutidas, incluindo ir além do FinFET para estruturas Gate-All-Around, ou até estruturas 2D de nano-folha, antes de eventualmente deixar o CMOS completamente. Nas perguntas e respostas no final da apresentação, o Dr. Mayberry afirmou que espera que os transistores de nanofios estejam em produção de alto volume dentro de cinco anos, colocando uma marca muito distinta na areia para a Intel e outros.

Os transistores com aletas, como introduzidos pela Intel em '22nm' e todos os outros em '16nm', eram uma maneira de escalar a corrente do inversor além de um transistor plano, uma métrica essencial para permitir a lógica de densidade e alto desempenho. Atualmente, a Intel está em seu projeto FinFET de várias gerações, com cada geração aumentando a altura das aletas, a fim de ajudar a impulsionar as principais métricas. Entretanto, como nos transistores planares, existe um limite entre um limite natural e um limite de fabricação, onde é necessária outra mudança no projeto do transistor. Nesse caso, os projetos Gate-All-Around, que estão em pesquisa e desenvolvimento há mais de uma década ou mais, ou são necessários.

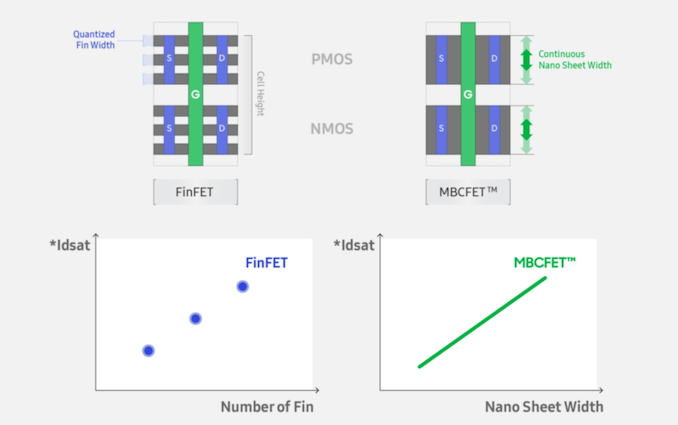

Existem vários nomes diferentes para os designs Gate-All-Around (GAA). A implementação do GAA basicamente se parece com uma aleta do transistor pairando, que pode ser realmente pequena (nanofios) ou mais larga (nanoparticula), com vários fios ou folhas empilhados aumentando a largura efetiva do transistor quando se trata de direcionar as métricas atuais. O FinFET, para a maioria das empresas de fundição, espera interceptar o nó '3nm', que deve oferecer densidade semelhante ao 'nó 5nm' da Intel.

Um dos principais benefícios desses transistores GAA é que o transistor pode ser especificamente adaptado aos requisitos operacionais. Um transistor típico com um FinFET pode exigir uma altura de célula de 6-7 aletas discretas e, portanto, a corrente do inversor é uma função da contagem de aletas. Com um design do tipo GAA, não apenas implementando o empilhamento, mas também a largura da folha, a corrente do inversor é agora um espectro contínuo, o que deve permitir economia de espaço e economia de energia em nível de silício. Enquanto os FinFETs têm apenas um ponto de design de potência / frequência em um design de nó de processo para uma determinada contagem de aletas, o GAA permite uma escala contínua no design de transistores.

A Samsung já anunciou sua intenção de entregar transistores GAA em seu processo de fabricação no estágio em que atinge um nó de processo '3nm'. Em maio de 2019, a empresa divulgou um comunicado à imprensa como parte de seu Fórum de Fundição que a primeira versão beta do PDK, v0.1, estava pronta para seus clientes de fundição começarem a experimentar. Na época, a Samsung esperava que as primeiras execuções de teste do seu processo 3GAE fossem encerradas em 2020, com produção de risco no final de 2020 e produção de volume no final de 2021.

Durante os Simpósios VLSI de 2020 sobre Tecnologia e Circuitos, CTO da Intel e GM do Intel Labs, o Dr. Mike Mayberry fez uma das palestras plenárias sobre 'O Futuro da Computação'. Na apresentação detalhada, o Dr. Mayberry abordou bastante sobre como a computação está permeando em todos os níveis, do dispositivo à extremidade do datacenter, e como a demanda por baixa latência e alto desempenho são elementos-chave para impulsionar essa mudança. Com isso vem uma série de opções e oportunidades de design, mas também barreiras de complexidade, custo e computação. Um dos requisitos para conduzir mudanças de paradigma é a mudança no nível de fabricação, indo além da tecnologia FinFET, quando esperamos que todas as principais fundições de ponta comecem a introduzir a tecnologia GAA. O Dr. Mayberry abordou arquiteturas específicas do domínio, gerenciamento de memória e energia, segurança, complexidade do sistema,

Havia alguns slides que poderiam valer a pena serem abordados em um artigo futuro, juntamente com algumas das partes de perguntas e respostas, mas foi nessa questão que Mayberry disse um ponto que vale a pena relatar.

Aqui está o nosso vídeo da discussão:

É difícil não dar dicas sobre roteiros e cronogramas ao afirmar quando uma determinada tecnologia estará pronta; portanto, apesar do Dr. Mayberry afirmar que ele seria vago, isso meio que nos ajuda a restringir alguns dos planos da Intel.

Vale ressaltar que nem a pergunta nem o Dr. Mayberry disseram que esse era um cronograma previsto para a implementação da Intel, e ele poderia estar falando mais sobre os concorrentes da Intel. No entanto, nesses tipos de conversas, discutir a concorrência costuma ser muito criticado internamente; é por isso que temos a impressão de que isso se concentrou mais na capacidade da Intel de produzir GAA do que qualquer outra pessoa.

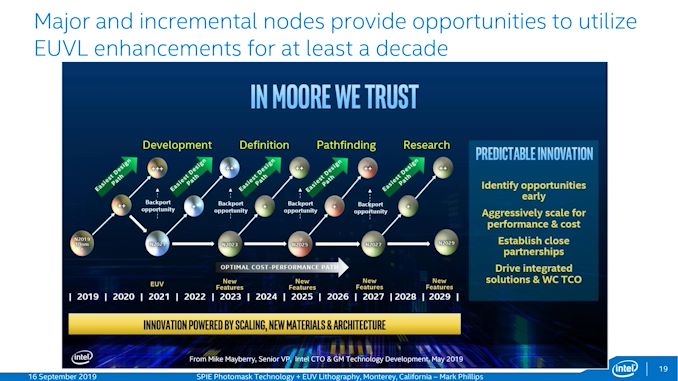

Dado o que sabemos sobre a linha do tempo da Intel, temos este slide da Intel, conforme apresentado em setembro de 2019 na conferência da SPIE:

Para 2021, a Intel está preparando 10 +++ e um novo nó de processo (7nm), e sabemos que esse é o caso, uma vez que a Intel possui um contrato com o supercomputador Aurora para Argonne , que deve ter a nova Ponte da Intel Acelerador Vecchio HPC no interior, que é parcialmente construído em 7nm. Esse sistema precisa ser entregue em 2021, ou pelo menos a Intel deve atingir uma série de marcos mínimos para esse sistema em 2021, para que possamos ver as primeiras impressões de 7nm naquele momento. O slide acima também diz 7nm no EUV.

Supondo que tudo corra como planejado, temos 2022 com 7+, 2023 com 7 ++ e outro novo nó do processo, que se acredita ser de 5nm. Espera-se que este seja o ponto de inflexão dos 3nm do TSMC em termos de densidade, o que poderia sugerir que é aqui que é provável que a tecnologia GAA esteja.

Indo além disso, 2024 é 5+, depois 2025 é 5 ++ e 3nm. Se eu fosse um apostador, e previsse que a linha do tempo da Intel ao longo de cinco anos poderia passar a maior parte de 6 a 12 meses, então 2025 ainda estaria na era de 5nm / 5+. Portanto, com o Dr. Mayberry dizendo dentro de 5 anos por alto volume, o dinheiro inteligente seria o GAA chegando a 5 nm, em 2023-2024.

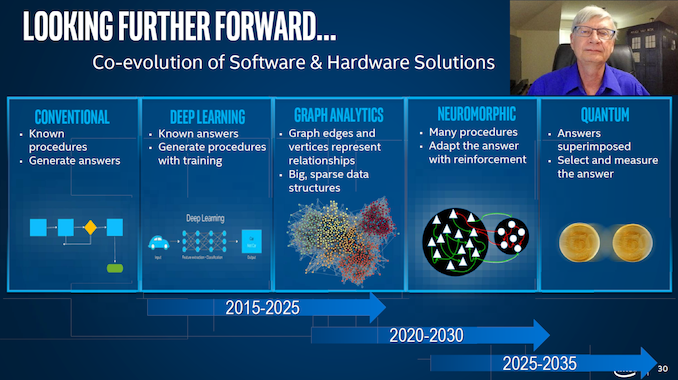

Este foi um dos slides finais da apresentação, mostrando para onde a Intel está olhando nos próximos 15 anos. A Quantum está tão fora do escopo de qualquer outra coisa que a Intel esteja fazendo que o Dr. Mayberry disse que está tão distante neste momento. No entanto, a Intel está dando passos em direção à aprendizagem profunda, análise gráfica e computação neuromorófica.

@user101 @dayllann

Intel to use Nanowire/Nanoribbon Transistors in Volume ‘in Five Years’

Este ano, na conferência internacional do VLSI, o CTO da Intel, Mike Mayberry, fez uma das apresentações plenárias, que este ano foi intitulada 'O Futuro da Computação'. Dentro da apresentação, várias novas tecnologias de fabricação foram discutidas, incluindo ir além do FinFET para estruturas Gate-All-Around, ou até estruturas 2D de nano-folha, antes de eventualmente deixar o CMOS completamente. Nas perguntas e respostas no final da apresentação, o Dr. Mayberry afirmou que espera que os transistores de nanofios estejam em produção de alto volume dentro de cinco anos, colocando uma marca muito distinta na areia para a Intel e outros.

Os transistores com aletas, como introduzidos pela Intel em '22nm' e todos os outros em '16nm', eram uma maneira de escalar a corrente do inversor além de um transistor plano, uma métrica essencial para permitir a lógica de densidade e alto desempenho. Atualmente, a Intel está em seu projeto FinFET de várias gerações, com cada geração aumentando a altura das aletas, a fim de ajudar a impulsionar as principais métricas. Entretanto, como nos transistores planares, existe um limite entre um limite natural e um limite de fabricação, onde é necessária outra mudança no projeto do transistor. Nesse caso, os projetos Gate-All-Around, que estão em pesquisa e desenvolvimento há mais de uma década ou mais, ou são necessários.

Existem vários nomes diferentes para os designs Gate-All-Around (GAA). A implementação do GAA basicamente se parece com uma aleta do transistor pairando, que pode ser realmente pequena (nanofios) ou mais larga (nanoparticula), com vários fios ou folhas empilhados aumentando a largura efetiva do transistor quando se trata de direcionar as métricas atuais. O FinFET, para a maioria das empresas de fundição, espera interceptar o nó '3nm', que deve oferecer densidade semelhante ao 'nó 5nm' da Intel.

Um dos principais benefícios desses transistores GAA é que o transistor pode ser especificamente adaptado aos requisitos operacionais. Um transistor típico com um FinFET pode exigir uma altura de célula de 6-7 aletas discretas e, portanto, a corrente do inversor é uma função da contagem de aletas. Com um design do tipo GAA, não apenas implementando o empilhamento, mas também a largura da folha, a corrente do inversor é agora um espectro contínuo, o que deve permitir economia de espaço e economia de energia em nível de silício. Enquanto os FinFETs têm apenas um ponto de design de potência / frequência em um design de nó de processo para uma determinada contagem de aletas, o GAA permite uma escala contínua no design de transistores.

A Samsung já anunciou sua intenção de entregar transistores GAA em seu processo de fabricação no estágio em que atinge um nó de processo '3nm'. Em maio de 2019, a empresa divulgou um comunicado à imprensa como parte de seu Fórum de Fundição que a primeira versão beta do PDK, v0.1, estava pronta para seus clientes de fundição começarem a experimentar. Na época, a Samsung esperava que as primeiras execuções de teste do seu processo 3GAE fossem encerradas em 2020, com produção de risco no final de 2020 e produção de volume no final de 2021.

Durante os Simpósios VLSI de 2020 sobre Tecnologia e Circuitos, CTO da Intel e GM do Intel Labs, o Dr. Mike Mayberry fez uma das palestras plenárias sobre 'O Futuro da Computação'. Na apresentação detalhada, o Dr. Mayberry abordou bastante sobre como a computação está permeando em todos os níveis, do dispositivo à extremidade do datacenter, e como a demanda por baixa latência e alto desempenho são elementos-chave para impulsionar essa mudança. Com isso vem uma série de opções e oportunidades de design, mas também barreiras de complexidade, custo e computação. Um dos requisitos para conduzir mudanças de paradigma é a mudança no nível de fabricação, indo além da tecnologia FinFET, quando esperamos que todas as principais fundições de ponta comecem a introduzir a tecnologia GAA. O Dr. Mayberry abordou arquiteturas específicas do domínio, gerenciamento de memória e energia, segurança, complexidade do sistema,

Havia alguns slides que poderiam valer a pena serem abordados em um artigo futuro, juntamente com algumas das partes de perguntas e respostas, mas foi nessa questão que Mayberry disse um ponto que vale a pena relatar.

P: Você pode nos fornecer o cronograma para a introdução da tecnologia de processo de nanofibras / nanofios na produção de alto volume?

R: Não se trata de um roteiro, por isso vou ser vago e dizer dentro dos próximos cinco anos.

Aqui está o nosso vídeo da discussão:

É difícil não dar dicas sobre roteiros e cronogramas ao afirmar quando uma determinada tecnologia estará pronta; portanto, apesar do Dr. Mayberry afirmar que ele seria vago, isso meio que nos ajuda a restringir alguns dos planos da Intel.

Vale ressaltar que nem a pergunta nem o Dr. Mayberry disseram que esse era um cronograma previsto para a implementação da Intel, e ele poderia estar falando mais sobre os concorrentes da Intel. No entanto, nesses tipos de conversas, discutir a concorrência costuma ser muito criticado internamente; é por isso que temos a impressão de que isso se concentrou mais na capacidade da Intel de produzir GAA do que qualquer outra pessoa.

Dado o que sabemos sobre a linha do tempo da Intel, temos este slide da Intel, conforme apresentado em setembro de 2019 na conferência da SPIE:

Para 2021, a Intel está preparando 10 +++ e um novo nó de processo (7nm), e sabemos que esse é o caso, uma vez que a Intel possui um contrato com o supercomputador Aurora para Argonne , que deve ter a nova Ponte da Intel Acelerador Vecchio HPC no interior, que é parcialmente construído em 7nm. Esse sistema precisa ser entregue em 2021, ou pelo menos a Intel deve atingir uma série de marcos mínimos para esse sistema em 2021, para que possamos ver as primeiras impressões de 7nm naquele momento. O slide acima também diz 7nm no EUV.

Supondo que tudo corra como planejado, temos 2022 com 7+, 2023 com 7 ++ e outro novo nó do processo, que se acredita ser de 5nm. Espera-se que este seja o ponto de inflexão dos 3nm do TSMC em termos de densidade, o que poderia sugerir que é aqui que é provável que a tecnologia GAA esteja.

Indo além disso, 2024 é 5+, depois 2025 é 5 ++ e 3nm. Se eu fosse um apostador, e previsse que a linha do tempo da Intel ao longo de cinco anos poderia passar a maior parte de 6 a 12 meses, então 2025 ainda estaria na era de 5nm / 5+. Portanto, com o Dr. Mayberry dizendo dentro de 5 anos por alto volume, o dinheiro inteligente seria o GAA chegando a 5 nm, em 2023-2024.

Este foi um dos slides finais da apresentação, mostrando para onde a Intel está olhando nos próximos 15 anos. A Quantum está tão fora do escopo de qualquer outra coisa que a Intel esteja fazendo que o Dr. Mayberry disse que está tão distante neste momento. No entanto, a Intel está dando passos em direção à aprendizagem profunda, análise gráfica e computação neuromorófica.

@user101 @dayllann

Documentação da Intel 12ª geração Alder Lake-S 10nm +++ lançada: para competir com CPUs Ryzen de 5nm baseadas em Zen 4

www.hardwaretimes.com

www.hardwaretimes.com

Os documentos de design e os drivers dos processadores de desktop Intel 12th Gen Alder Lake-S da Intel estão sendo compartilhados entre desenvolvedores e parceiros do conselho.

Embora o arquivo em si não lance muita luz sobre o processador, além do soquete: LGA1700, sabemos várias coisas sobre o primeiro processador de desktop de 10 nm da Intel. Em primeiro lugar, há rumores de que ele se baseia na terceira iteração do nó de 10nm (10nm +++) e aproveitará a enseada de Golden Cove (sucessora de Willow Cove, que alimenta o Tiger Lake). Como tal, será um chip significativamente mais rápido em comparação com as peças da 10ª geração do cometa Lake-S, que ainda usam o núcleo Skylake de 5 anos (14nm).

Um IPC maciço e relógios centrais de até 5 GHz, graças a uma forma mais madura do processo de 10 nm, significa que a Intel deve ser capaz de manter seus jogos e a liderança de thread único sobre a AMD. Ou, no mínimo, com os processadores Ryzen baseados em Zen 3 / Zen 4. É interessante notar que, até então, o AMd terá se mudado para o nó de 5nm, portanto ainda terá uma vantagem em termos de eficiência e liderança de processo.

O Alder Lake deve aterrissar em 2022.

Especialista da Intel afirma que finalmente perdeu a Apple porque o Skylake QA 'era anormalmente ruim'

Intel 12th Gen Alder Lake-S 10nm+++ Documentation Released: To Compete with 5nm Zen 4 Based Ryzen CPUs | Hardware Times

The design documents and drivers for Intel’s 12th Gen Alder Lake-S desktop processors are reportedly being shared among developers and board partners. While the file itself doesn’t shed much light on the processor, other than the socket: LGA1700, we know multiple things about Intel’s first 10nm...

www.hardwaretimes.com

www.hardwaretimes.com

Os documentos de design e os drivers dos processadores de desktop Intel 12th Gen Alder Lake-S da Intel estão sendo compartilhados entre desenvolvedores e parceiros do conselho.

Embora o arquivo em si não lance muita luz sobre o processador, além do soquete: LGA1700, sabemos várias coisas sobre o primeiro processador de desktop de 10 nm da Intel. Em primeiro lugar, há rumores de que ele se baseia na terceira iteração do nó de 10nm (10nm +++) e aproveitará a enseada de Golden Cove (sucessora de Willow Cove, que alimenta o Tiger Lake). Como tal, será um chip significativamente mais rápido em comparação com as peças da 10ª geração do cometa Lake-S, que ainda usam o núcleo Skylake de 5 anos (14nm).

Um IPC maciço e relógios centrais de até 5 GHz, graças a uma forma mais madura do processo de 10 nm, significa que a Intel deve ser capaz de manter seus jogos e a liderança de thread único sobre a AMD. Ou, no mínimo, com os processadores Ryzen baseados em Zen 3 / Zen 4. É interessante notar que, até então, o AMd terá se mudado para o nó de 5nm, portanto ainda terá uma vantagem em termos de eficiência e liderança de processo.

O Alder Lake deve aterrissar em 2022.

--- Post duplo é unido automaticamente: ---

Especialista da Intel afirma que finalmente perdeu a Apple porque o Skylake QA 'era anormalmente ruim'

Última edição:

CPUs de desktop Intel 12th Gen Alder Lake-S para oferecer suporte ao soquete LGA 1700 com memória DDR5

wccftech.com

wccftech.com

Alder Lake is going to utilize a BIG little core strategy, integrating both Golden Cove and Gracemont cores on a single-chip while also featuring next-generation Xe enhanced graphics engine.

Aside from the new CPUs, Intel's LGA 1700 is aiming to be the first platform to hit the market shelves with DDR5 support. In the previous post, leaks hinted at up to DDR5-4800 native memory support on 6-layer and DDR5-4000 on the 4-layer motherboards. This would mark a huge jump over the current native speeds of DDR4-2933 MHz.

Intel Rocket Lake Desktop CPU With 8 Cores, 16 Threads Benchmarked, Up To 4.30 GHz Clocks & 32 EU Xe Graphics

wccftech.com

wccftech.com

Intel 12th Gen Alder Lake-S Desktop CPUs To Feature Support on LGA 1700 Socket With DDR5 Memory

It looks like Intel has confirmed that its next-gen Alder Lake-S desktop CPUs will be featuring support on the new LGA 1700 socket.

Alder Lake is going to utilize a BIG little core strategy, integrating both Golden Cove and Gracemont cores on a single-chip while also featuring next-generation Xe enhanced graphics engine.

Aside from the new CPUs, Intel's LGA 1700 is aiming to be the first platform to hit the market shelves with DDR5 support. In the previous post, leaks hinted at up to DDR5-4800 native memory support on 6-layer and DDR5-4000 on the 4-layer motherboards. This would mark a huge jump over the current native speeds of DDR4-2933 MHz.

Intel Rocket Lake Desktop CPU With 8 Cores, 16 Threads Benchmarked, Up To 4.30 GHz Clocks & 32 EU Xe Graphics

Intel Rocket Lake Desktop CPU With 8 Cores, 16 Threads Benchmarked, Up To 4.30 GHz Clocks & 32 EU Xe Graphics

A new entry of Intel's Rocket Lake Desktop CPU has been spotted which shows an 8 core and 16 thread chip at 4.3 GHz with Xe graphics.

Nao to conseguindo enxergar como INTEL vai competir com zen 4 com essa configuração estranha, para as CPUs em mobile até entendo mas em desktop não consigo ver vantagem em 8 núcleos rápidos + 8 núcleos menores mais lentos .CPUs de desktop Intel 12th Gen Alder Lake-S para oferecer suporte ao soquete LGA 1700 com memória DDR5

Intel 12th Gen Alder Lake-S Desktop CPUs To Feature Support on LGA 1700 Socket With DDR5 Memory

It looks like Intel has confirmed that its next-gen Alder Lake-S desktop CPUs will be featuring support on the new LGA 1700 socket.wccftech.com

Alder Lake is going to utilize a BIG little core strategy, integrating both Golden Cove and Gracemont cores on a single-chip while also featuring next-generation Xe enhanced graphics engine.

Aside from the new CPUs, Intel's LGA 1700 is aiming to be the first platform to hit the market shelves with DDR5 support. In the previous post, leaks hinted at up to DDR5-4800 native memory support on 6-layer and DDR5-4000 on the 4-layer motherboards. This would mark a huge jump over the current native speeds of DDR4-2933 MHz.

Intel Rocket Lake Desktop CPU With 8 Cores, 16 Threads Benchmarked, Up To 4.30 GHz Clocks & 32 EU Xe Graphics

Intel Rocket Lake Desktop CPU With 8 Cores, 16 Threads Benchmarked, Up To 4.30 GHz Clocks & 32 EU Xe Graphics

A new entry of Intel's Rocket Lake Desktop CPU has been spotted which shows an 8 core and 16 thread chip at 4.3 GHz with Xe graphics.wccftech.com

Falam que o ipc sera grandioso e sera suficiente para competir com zen 4 , só que não existe nenhuma informação do que teremos no zen 4 seu ipc contagem de núcleos clock , mau temos todos os dados do zen 3, AMD ta muita agressiva na evolução.

Teve uns rumores que

zen 3 seria teria 15% mais IPC que o já bom IPC do zen 2

zen 4 ?? novamente mais 15 % novo no 5nm + núcleos??

Sei la posso estar muito errado , mas esta muito nebuloso essa estategia da Intel.

Segundo um slide da AMD, o Zen 3 terá ~10% de aumento de IPC em cima do Zen 2.Nao to conseguindo enxergar como INTEL vai competir com zen 4 com essa configuração estranha, para as CPUs em mobile até entendo mas em desktop não consigo ver vantagem em 8 núcleos rápidos + 8 núcleos menores mais lentos .

Falam que o ipc sera grandioso e sera suficiente para competir com zen 4 , só que não existe nenhuma informação do que teremos no zen 4 seu ipc contagem de núcleos clock , mau temos todos os dados do zen 3, AMD ta muita agressiva na evolução.

Teve uns rumores que

zen 3 seria teria 15% mais IPC que o já bom IPC do zen 2

zen 4 ?? novamente mais 15 % novo no 5nm + núcleos??

Sei la posso estar muito errado , mas esta muito nebuloso essa estategia da Intel.

Li que essa arquitetura aí ia vir com uns 80% de IPC em cima do Skylake, porém com clocks mais baixos no começo.

Users who are viewing this thread

Total: 2 (membros: 0, visitantes: 2)