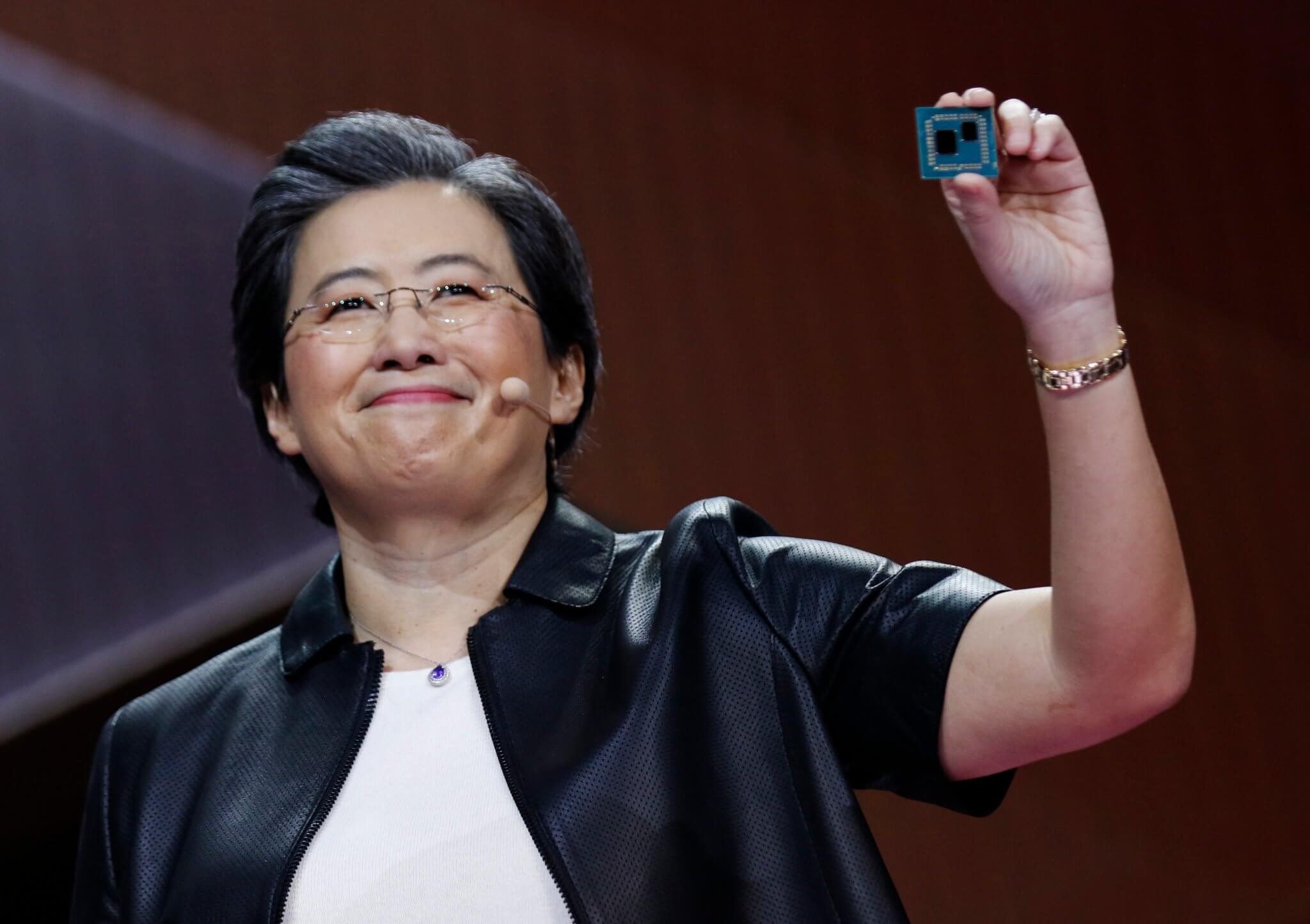

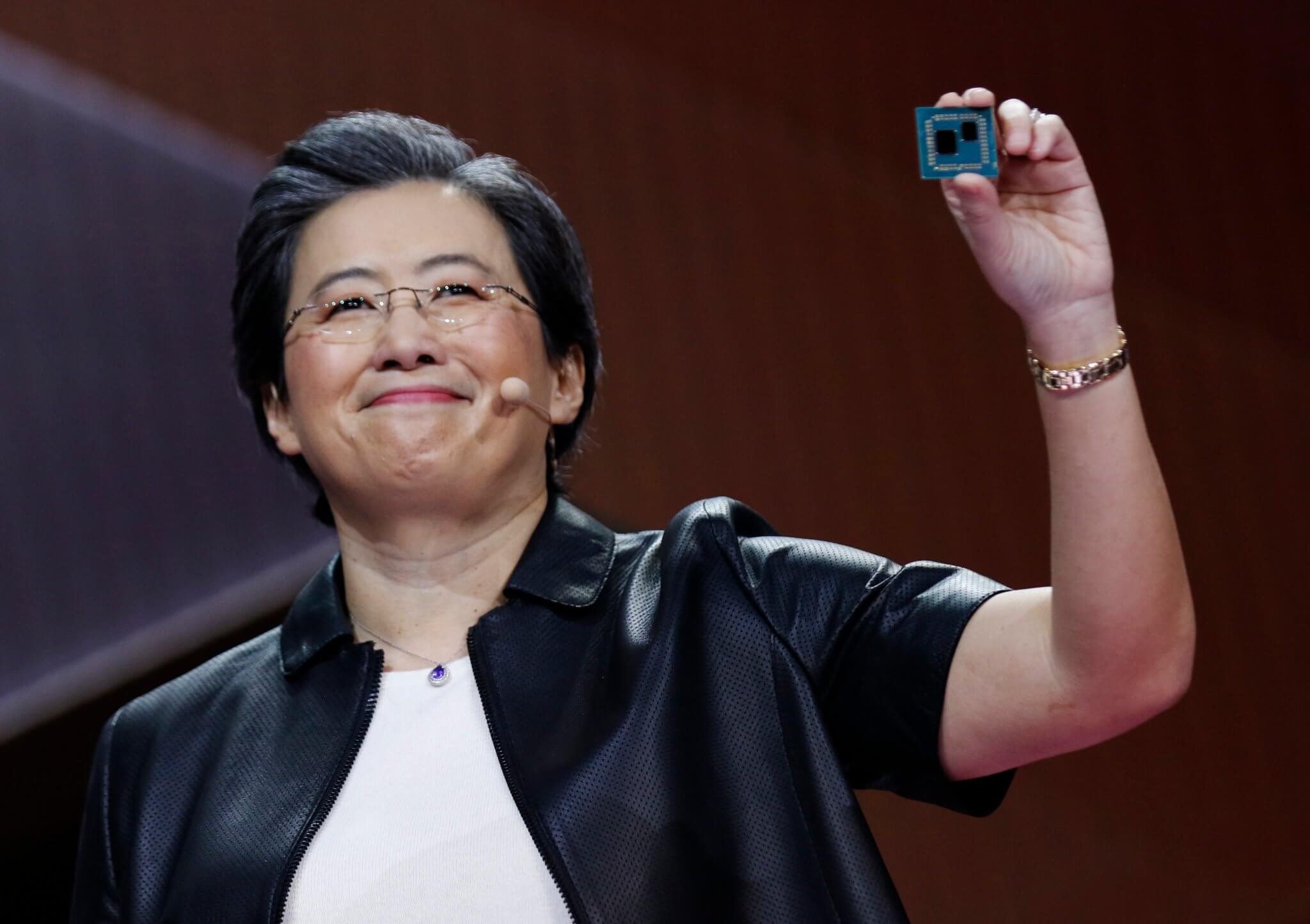

Os produtos AMD agora representam mais de 50% das vendas de CPU premium

Corroendo a participação de mercado da Intel por dez trimestres consecutivos

www.techspot.com

www.techspot.com

Ilustrando a popularidade dos processadores da team red, uma pesquisa mostrou que eles eram os preferidos por 60% dos europeus . Há também o fato de que as dez CPUs mais vendidas da Amazon nos EUA consistem em oito produtos AMD.

AMD investe pesadamente em P&D - Gastos crescem mais de 18% A / A

É uma loucura quando você pensa que o orçamento de P&D da Intel e da Apple para um mês é basicamente um ano inteiro para a AMD.

Vamos lá

A Intel tem suas próprias fábricas, o que significa que elas precisam de pesquisa e desenvolvimento lá

Seus próprios chips wifi / 4g / 5g etc.

Comutadores próprios, chips de 1gbps

SSDs próprios, unidades optane

Eles gastam quase o mesmo em pesquisa e desenvolvimento que a Samsung, que faz tudo o que você acabou de mencionar, além de TVs com memória, geladeiras, telefones, tablets, material de home theater, tablets que assistem equipamentos médicos e mais

Edit: parece que o equipamento médico não está incluído nessa pesquisa e desenvolvimento, mas praticamente tudo o que mencionei é.

A Samsung Electronics é uma empresa multinacional de eletrônicos e tecnologia da informação com sede em Suwon e a principal empresa do grupo Samsung.

Seus produtos incluem condicionadores de ar, computadores, televisões digitais, diodos orgânicos emissores de luz de matriz ativa (AMOLEDs), telefones celulares, monitores, impressoras, geladeiras, semicondutores e equipamentos de rede de telecomunicações.

É a maior fabricante de celulares do mundo em vendas unitárias no primeiro trimestre de 2012, com uma participação de mercado global de 25,4%. É também a segunda maior fabricante de semicondutores do mundo em receitas de 2011 (depois da Intel).

Lembro-me de ver um gráfico em algum lugar que mostrava quanto as empresas estão gastando em P&D como uma porcentagem do orçamento total. Certamente a Nvidia estava no topo, seguida de perto pela AMD e Intel em último lugar. Embora a Intel tenha um orçamento enorme, seus gastos reais em pesquisa e desenvolvimento em termos de dólares devem ser significativamente maiores que a Nvidia / AMD combinada.

Parece que as empresas de CPU / GPU, em particular, estão gastando muito mais em P&D do que outras empresas de TI (porcentagem).

É 18% A / A, mas subiu 60% em relação ao lançamento do Ryzen 1 para a AMD, o que apenas mostra como o dinheiro estava com fome e o que um pouco de impulso pode fazer.

Esperamos ver isso no espaço da GPU agora.

A AMD também acabou de pagar suas maiores obrigações de dívida, por isso espero que os orçamentos de P&D continuem aumentando à medida que a ameaça de falência é cada vez mais distante no espelho retrovisor.

Corroendo a participação de mercado da Intel por dez trimestres consecutivos

AMD products now account for over 50% of premium CPU sales

Last year brought several indicators that AMD was taking the fight to Intel in the desktop CPU space, having seen its market share increase every quarter since...

www.techspot.com

www.techspot.com

Ilustrando a popularidade dos processadores da team red, uma pesquisa mostrou que eles eram os preferidos por 60% dos europeus . Há também o fato de que as dez CPUs mais vendidas da Amazon nos EUA consistem em oito produtos AMD.

AMD investe pesadamente em P&D - Gastos crescem mais de 18% A / A

É uma loucura quando você pensa que o orçamento de P&D da Intel e da Apple para um mês é basicamente um ano inteiro para a AMD.

Vamos lá

A Intel tem suas próprias fábricas, o que significa que elas precisam de pesquisa e desenvolvimento lá

Seus próprios chips wifi / 4g / 5g etc.

Comutadores próprios, chips de 1gbps

SSDs próprios, unidades optane

Eles gastam quase o mesmo em pesquisa e desenvolvimento que a Samsung, que faz tudo o que você acabou de mencionar, além de TVs com memória, geladeiras, telefones, tablets, material de home theater, tablets que assistem equipamentos médicos e mais

Edit: parece que o equipamento médico não está incluído nessa pesquisa e desenvolvimento, mas praticamente tudo o que mencionei é.

A Samsung Electronics é uma empresa multinacional de eletrônicos e tecnologia da informação com sede em Suwon e a principal empresa do grupo Samsung.

Seus produtos incluem condicionadores de ar, computadores, televisões digitais, diodos orgânicos emissores de luz de matriz ativa (AMOLEDs), telefones celulares, monitores, impressoras, geladeiras, semicondutores e equipamentos de rede de telecomunicações.

É a maior fabricante de celulares do mundo em vendas unitárias no primeiro trimestre de 2012, com uma participação de mercado global de 25,4%. É também a segunda maior fabricante de semicondutores do mundo em receitas de 2011 (depois da Intel).

Lembro-me de ver um gráfico em algum lugar que mostrava quanto as empresas estão gastando em P&D como uma porcentagem do orçamento total. Certamente a Nvidia estava no topo, seguida de perto pela AMD e Intel em último lugar. Embora a Intel tenha um orçamento enorme, seus gastos reais em pesquisa e desenvolvimento em termos de dólares devem ser significativamente maiores que a Nvidia / AMD combinada.

Parece que as empresas de CPU / GPU, em particular, estão gastando muito mais em P&D do que outras empresas de TI (porcentagem).

É 18% A / A, mas subiu 60% em relação ao lançamento do Ryzen 1 para a AMD, o que apenas mostra como o dinheiro estava com fome e o que um pouco de impulso pode fazer.

Esperamos ver isso no espaço da GPU agora.

A AMD também acabou de pagar suas maiores obrigações de dívida, por isso espero que os orçamentos de P&D continuem aumentando à medida que a ameaça de falência é cada vez mais distante no espelho retrovisor.