Vocês estão achando isso ruim essa degradação no 7nm ?

Imagina com o 5nm em diante

Ninguém vai escapar desse problema, seja a NVIDIA, INTEL ou a AMD

Problemas de envelhecimento em 5nm e abaixo

Semiconductor aging has moved from being a foundry issue to a user problem. As we get to 5nm and below, vectorless methodologies become too inaccurate.

semiengineering.com

O envelhecimento dos semicondutores passou de um problema de fundição para um problema do usuário. Quando chegamos a 5 nm e abaixo, as metodologias sem vetor se tornam muito imprecisas.

Os mecanismos que causam o envelhecimento em semicondutores são conhecidos há muito tempo, mas o conceito não preocupava a maioria das pessoas porque o tempo de vida útil esperado das peças era muito mais longo do que a implantação pretendida em campo. Em um curto período de tempo, tudo isso mudou.

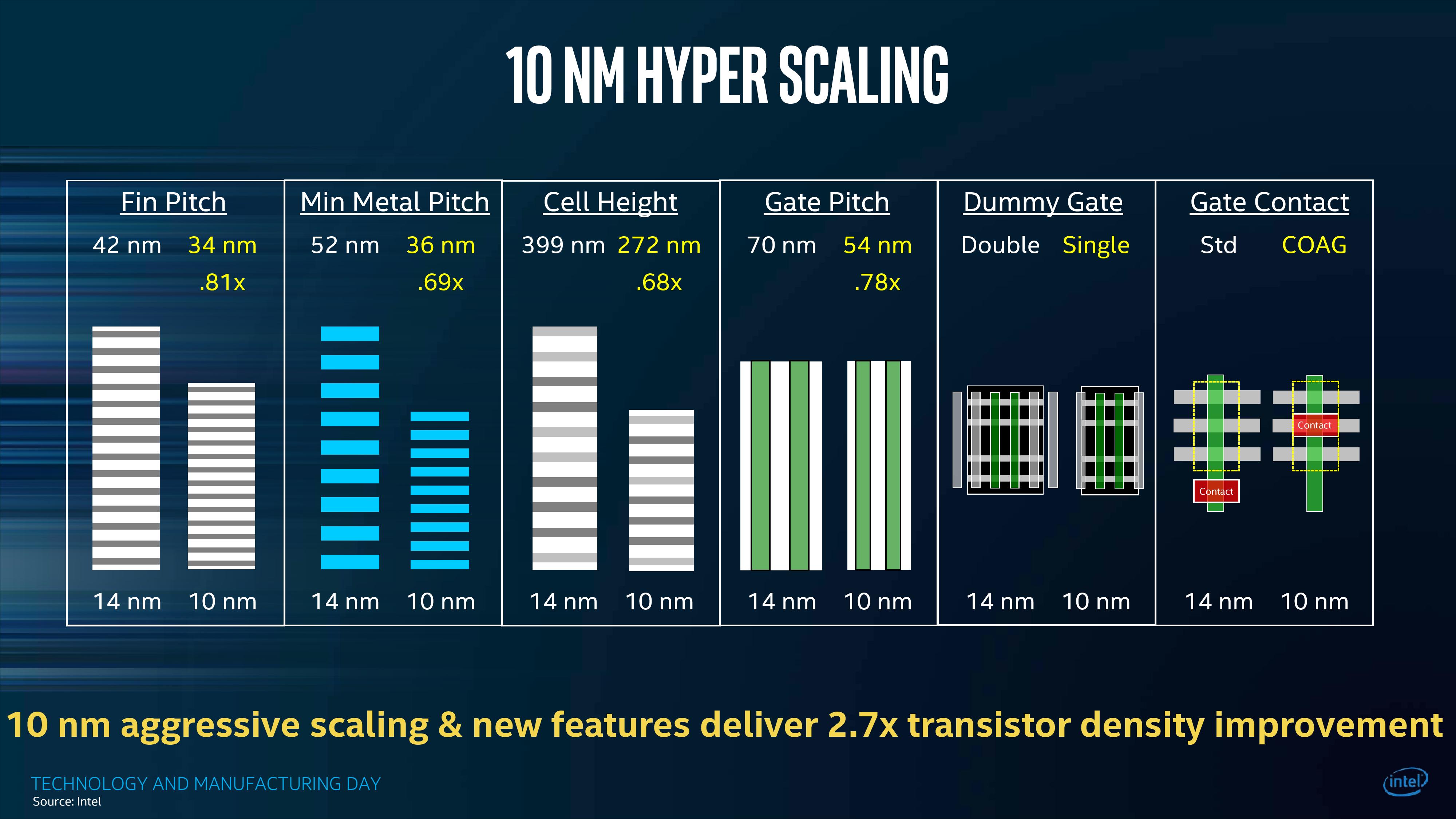

À medida que as geometrias dos dispositivos se tornam menores, o problema se torna mais significativo. Com 5 nm, torna-se uma parte essencial do fluxo de desenvolvimento, com ferramentas e fluxos evoluindo rapidamente à medida que novos problemas são descobertos, compreendidos e modelados.

"Vimos que ela passou de uma tecnologia boutique, usada por grupos de design específicos, para algo que é muito mais uma parte regular do processo de assinatura", diz Art Schaldenbrand, gerente de produtos sênior da

Cadence . “À medida que entramos nesses nós mais avançados, o número de problemas com os quais você precisa lidar aumenta. Com meio mícron, você pode ter que se preocupar apenas com a injeção de portador quente (HCI) se estiver fazendo algo como um chip de energia. À medida que você desce abaixo de 180 nm, você começa a ver coisas como

instabilidade de temperatura de polarização negativa (NBTI). Mais abaixo, você entra em outros fenômenos, como o auto-aquecimento, que se torna um problema significativo de confiabilidade. ”

As formas de lidar com isso no passado não são mais viáveis. "Até recentemente, os designers lidavam de maneira muito conservadora com o problema do envelhecimento por excesso de design, deixando muita margem sobre a mesa", diz Ahmed Ramadan, gerente sênior de engenharia de produtos da

Mentor, uma empresa da Siemens . “No entanto, embora levar os projetos ao limite não seja apenas necessário para obter vantagem competitiva, também é necessário para atender aos novos requisitos de aplicações, devido aos benefícios reduzidos da escala do transistor. Tudo isso exige a necessidade de uma análise precisa do envelhecimento. ”

Enquanto novos fenômenos estão sendo descobertos, os antigos continuam a piorar. “Os fatores determinantes do envelhecimento, como temperatura e estresse elétrico, não mudaram realmente”, diz André Lange, gerente de grupo de qualidade e confiabilidade da Divisão de Engenharia de Sistemas Adaptativos da

Fraunhofer IIS . “No entanto, dispositivos ativos densamente compactados com margens mínimas de segurança são necessários para atender aos requisitos avançados de funcionalidade. Isso os torna mais suscetíveis a problemas de confiabilidade causados pelo autoaquecimento e pelo aumento da força do campo. Considerando as técnicas avançadas de empacotamento com integração 2.5D e 3D, os drivers para problemas de confiabilidade, especialmente temperatura, ganharão importância. ”

Fatores contribuintes

O maior fator é o calor. “Clocks mais altos tendem a produzir temperaturas mais altas e a temperatura é a maior causa de morte”, diz Rita Horner, gerente sênior de marketing de produtos para 3D-IC da

Synopsys .

“A temperatura exacerba a migração de elétrons. A vida esperada pode mudar exponencialmente de um pequeno delta de temperatura. ”

Isso se tornou uma preocupação muito maior com os

finFETs . "Em um processo CMOS plano, o calor pode escapar através da maior parte do dispositivo para o substrato com bastante facilidade", diz Schaldenbrand, da Cadence. "Mas quando você coloca o transistor de lado e o enrola em um cobertor, que é efetivamente como o óxido e o portão atuam, o canal experimenta um aumento de temperatura maior, de modo que o estresse que um dispositivo está enfrentando aumenta significativamente".

Uma quantidade crescente de eletrônicos está sendo implantada em ambientes hostis.

"Os chips semicondutores que operam em condições extremas, como automotivo (150 ° C) ou alta altitude (servidores de dados na Cidade do México) têm o maior risco de confiabilidade e restrições relacionadas ao envelhecimento", diz Milind Weling, vice-presidente sênior de programas e operações na Intermolecular. “

Os projetos

2.5D e

3D podem observar um estresse mecânico adicional nos chips de silicone subjacentes, e isso pode induzir o envelhecimento do estresse mecânico adicional.”

Os atributos dos dispositivos pioram progressivamente.

“Com o tempo, a tensão limite de um dispositivo diminui, o que significa que leva mais tempo para ligá-lo”, diz Haran Thanikasalam, engenheiro sênior de aplicativos para AMS da Synopsys. “Uma razão para isso é a instabilidade de viés negativa. Porém, à medida que os dispositivos diminuem, o dimensionamento da tensão tem sido mais lento que o dimensionamento da geometria.

Hoje, estamos atingindo os limites da física. Os dispositivos estão operando em torno de 0,6 a 0,7 volts a 3 nm, em comparação com 1,2 V a 40 nm ou 28 nm. Por esse motivo, os campos elétricos aumentaram. Um grande campo elétrico em uma área minúscula do dispositivo pode causar danos graves. ”

Isso é novo. "A maneira como capturamos esse fenômeno é algo chamado de ruptura dielétrica dependente do tempo (TTDB)", diz Schaldenbrand. "Você está vendo como essa densidade de campo causa a quebra dos dispositivos e certificando-se de que os dispositivos não estão com muita densidade de campo".

A outra causa primária do envelhecimento é a

eletromigração (EM). “Se você executar uma simulação de confiabilidade, como simulação de queda EM ou IR, não apenas os dispositivos se degradam, mas também a eletromigração nas interconexões”, acrescenta Thanikasalam. "Você precisa considerar não apenas os dispositivos, mas também as interconexões entre os dispositivos."

Analógico e digital

Quando se trata de envelhecimento, o digital é um subconjunto de analógico. "No digital, você está mais preocupado com a unidade, porque isso altera os atrasos de ascensão e queda", diz Schaldenbrand. “Isso cobre uma variedade de pecados. Mas o analógico é muito mais sutil e o ganho é algo com que você se preocupa. Só o fato de saber que o Vt mudou tanto não vai lhe dizer quanto o seu ganho será degradado. Essa é apenas uma parte da equação. ”

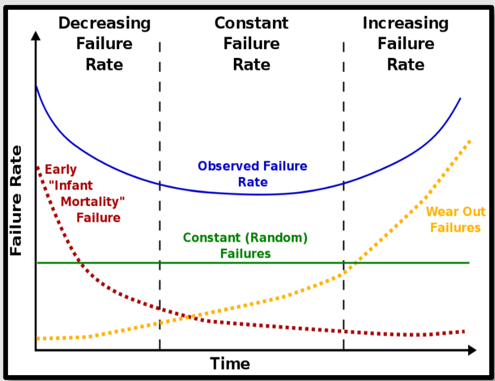

Fig 1 :

Falha dos componentes analógicos ao longo do tempo. Fonte: Synopsys

O envelhecimento pode ser mascarado em formato digital. "Dependendo da aplicação, um sistema pode apenas se degradar ou pode falhar com a mesma quantidade de envelhecimento", diz o Ramadan da Mentor.

“Por exemplo, a degradação do microprocessador pode levar a um desempenho mais baixo, necessitando de uma desaceleração, mas não de falhas necessárias. Em aplicativos de IA de missão crítica, como o ADAS, uma degradação do sensor pode levar diretamente a falhas de AI e, consequentemente, a falhas no sistema. ”

Essa noção mais simples de degradação para o digital muitas vezes pode ser ocultada. "Muito disso é capturado no nível de caracterização da célula", acrescenta Schaldenbrand. “Portanto, o projetista do sistema não se preocupa muito com isso. Se ele administra as bibliotecas certas, o problema é coberto por ele. ”

Ciclo de trabalho

Para obter uma imagem precisa do envelhecimento, é necessário considerar a atividade no design, mas geralmente isso não ocorre da maneira esperada. "A estabilidade negativa da temperatura de viés (NBTS) está afetando alguns dispositivos", diz Horner da Synopsys. “Mas os dispositivos não precisam estar funcionando ativamente. O envelhecimento pode estar acontecendo enquanto o dispositivo está desligado. ”

No passado, a análise era feita sem simulação. "Você só pode obter uma certa quantidade de dados de confiabilidade fazendo análises estáticas e independentes de vetores", diz Thanikasalam da Synopsys. “Essa análise não se importa com os estímulos que você dá ao seu sistema. Ele tem uma visão mais ampla e identifica onde os problemas estão acontecendo sem simular o design. Mas isso está provando ser uma maneira muito imprecisa de fazer as coisas, especialmente em nós menores, porque tudo depende da atividade. ”

Isso pode ser problemático para blocos de IP. "O problema é que, se alguém está criando seu próprio chip, seu próprio software em seu próprio dispositivo, ele tem todas as informações de que precisa, até o nível do transistor, qual é esse ciclo de trabalho", diz Kurt Shuler, vice-presidente de marketing na

Arteris IP . “Mas se você estiver criando um chip para o qual outras pessoas criarão software, ou se você estiver fornecendo um SDK inteiro e ele o estiver modificando, não saberá realmente. Esses fornecedores de chips precisam fornecer a seus clientes alguns meios para fazer essa análise. ”

Para algumas partes do projeto, os ciclos de serviço podem ser estimados. "Você nunca deseja encontrar um problema no nível do bloco no nível do sistema", diz Schaldenbrand. “As pessoas podem fazer a análise no nível do bloco, e é bastante barato fazer lá. Para um bloco analógico, como um ADC ou um SerDes ou um PLL, você tem uma boa idéia de qual será sua operação no sistema. Você sabe que tipo de estresse ele experimentará. Isso não é verdade para um grande design digital, onde você pode ter vários modos de operação. Isso mudará muito a atividade digital. ”

Esta é a razão fundamental pela qual ele se transformou em um problema do usuário.

“Isso coloca o ônus no usuário para garantir que você escolha estímulos que ativem as partes do design que você acha que serão mais vulneráveis ao envelhecimento e à eletromigração, e você deve fazer isso sozinho”, diz Thanikasalam.

“Isso criou um grande sinal de alerta entre os usuários finais, porque as fundições não serão capazes de fornecer estímulos. Eles não têm idéia do que seu design faz. ”

Monitoramento e teste

As abordagens do setor estão mudando em vários níveis.

“Para avaliar adequadamente o envelhecimento em um chip, os fabricantes confiaram em uma função chamada teste de queima, onde o wafer é cozida para envelhecê-la artificialmente, após a qual pode ser testada quanto à confiabilidade”, diz Syed Alam, líder global de semicondutores da Accenture .

"O calor é o principal fator para o envelhecimento em chips, com o uso por um segundo próximo, especialmente para flash, pois há tantas rescrições disponíveis em uma unidade".

E ainda é uma técnica na qual muitos confiam. "O AEC-Q100, um padrão importante para a eletrônica automotiva, contém vários testes que não revelam informações verdadeiras sobre a confiabilidade", diz Lange, da Fraunhofer. “Por exemplo, em testes de vida operacional em alta temperatura (HTOL), dispositivos 3 × 77 precisam ser estressados por 1000 horas com testes funcionais antes e depois do estresse. Mesmo quando todos os dispositivos passam, você não pode dizer se eles falharão após 1001 horas ou se durarão 10 vezes mais. Esta informação só pode ser obtida por testes prolongados ou simulações. ”

Uma alternativa emergente é incorporar sensores antigos no chip. “Existem sensores, que geralmente contêm um loop de tempo, e eles avisam quando leva mais tempo para os elétrons contornarem um loop”, diz Shuler da Arteris IP. “Existe também um conceito chamado células canárias, onde essas células são destinadas a morrer prematuramente em comparação com um transistor padrão. Isso pode lhe dizer que o envelhecimento está impactando o chip. O que você está tentando fazer é obter informações preditivas de que o chip vai morrer. Em alguns casos, eles estão pegando as informações desses sensores, tirando o chip, jogando-o em um grande banco de dados e executando algoritmos de IA para tentar realizar um trabalho preditivo. ”

Problemas adicionais em 3D

Muitos dos mesmos problemas existem nos projetos 2D, 2.5D e 3D, exceto que os problemas térmicos podem se tornar mais amplificados em algumas arquiteturas. Mas também pode haver um monte de novos problemas que ainda não foram totalmente compreendidos. “Quando você empilha dispositivos um sobre o outro, é necessário triturá-los para afiná-los”, diz Horner. “O estresse na die mais fina pode ser uma preocupação, e isso precisa ser entendido, estudado e tratado em termos de análise. Além disso, vários tipos de silício envelhecem de maneira diferente. Você está falando de um ambiente heterogêneo no qual está potencialmente empilhando DRAM, que tende a ser mais uma tecnologia específica - ou CPUs e GPUs, que podem utilizar nós de processos de tecnologia diferentes. Você pode ter diferentes tipos de

TSVs ou inchaços que foram usados neste silício em particular. Como eles interagem entre si?

Essas interfaces são uma preocupação. "Há um estresse no molde e isso altera as características do dispositivo", diz Schaldenbrand. “Mas se dies diferentes esquentarem para temperaturas diferentes, os locais onde eles fazem interface terão muito estresse mecânico. Esse é um grande problema, e a interconexão do sistema será um grande desafio no futuro. ”

Modelos e análises

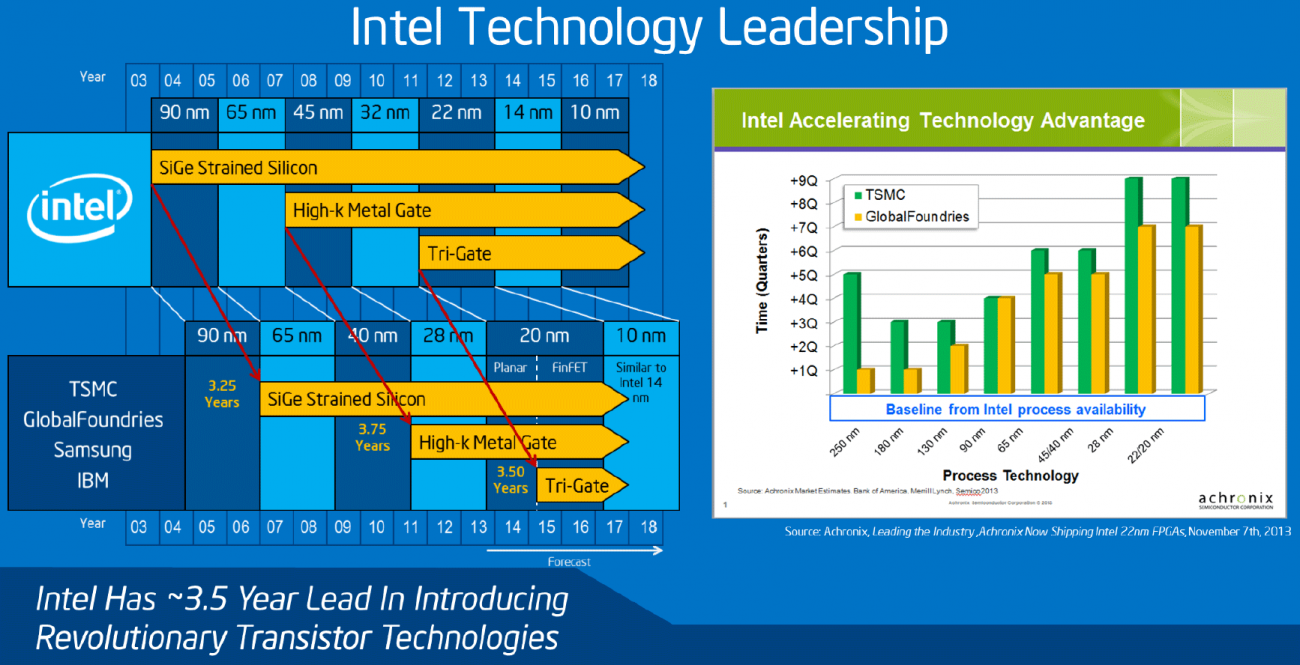

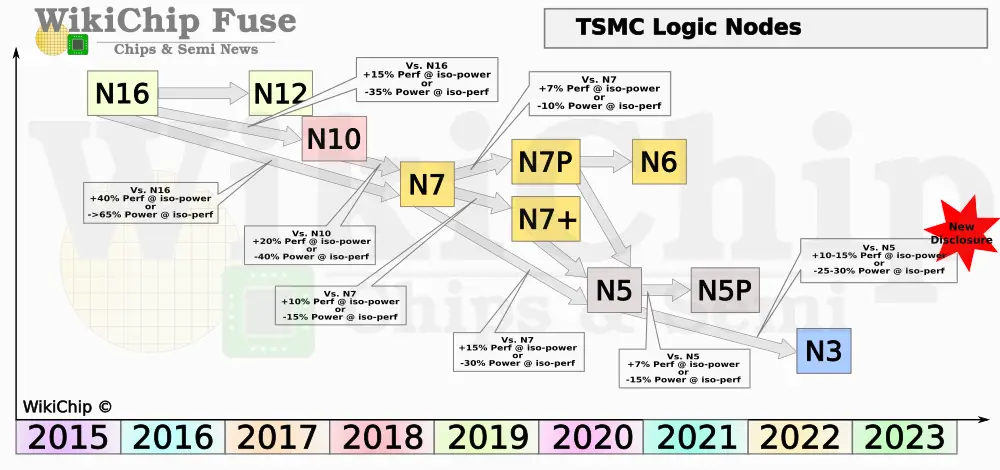

Tudo começa com as fundições. "Os TSMCs e os Samsungs do mundo precisam começar a fornecer essas informações", diz Shuler. "À medida que você atinge 5 nm e abaixo, mesmo 7 nm, há muita variabilidade nesses processos e isso piora tudo".

"As fundições se preocuparam com isso porque perceberam que os dispositivos sujeitos a campos elétricos mais altos estavam se degradando muito mais rápido do que antes", diz Thanikasalam. “Eles começaram a usar a solução de análise e confiabilidade MOS (MOSRA), que se aplica à parte antiga do dispositivo. Recentemente, vemos essa mudança em direção aos clientes finais que estão começando a usar os modelos de envelhecimento. Alguns clientes farão uma execução simples usando modelos degradados, de modo que a simulação represente a degradação da tensão limite. ”

Os chips de alto volume precisarão de análises muito mais extensas. “Para produção em grande volume, as simulações de PVT múltiplo estão se tornando uma maneira inútil de verificar isso”, acrescenta Thanikasalam. Todo mundo tem que rodar Monte Carlo nesse nível. A simulação de Monte Carlo com os modelos de variação é a chave em 5 nm e abaixo. ”

São necessários mais modelos. "Existem mais modelos sendo criados e otimizados", diz Horner. “Em termos de empilhamento 3D, temos conhecimento da preocupação com eletromigração, infravermelho, energia térmica e energia. Essas são as principais coisas que são entendidas e modeladas. Para os aspectos mecânicos - mesmo os materiais que colocamos entre as camadas e seus efeitos em termos de calor, e também as estruturas de estabilidade - enquanto existem modelos por aí, eles não são tão aprimorados porque ainda não vimos o suficiente deles . ”

Schaldenbrand concorda. “Estamos constantemente trabalhando nos modelos e atualizando-os, adicionando novos fenômenos à medida que as pessoas se conscientizam deles. Foram necessárias muitas alterações para se preparar para os nós avançados. Para o dispositivo nominal, podemos descrever muito bem o envelhecimento, mas a interação entre a variação do processo e seu efeito na confiabilidade ainda é um tópico de pesquisa. Esse é um assunto muito desafiador. ”

Com os finFETs, toda a metodologia mudou. “As regras se tornaram tão complicadas que você precisa de uma ferramenta que possa realmente interpretá-las, aplicá-las e nos dizer onde pode haver problemas daqui a dois, três anos”, diz Thanikasalam. "Os FinFETs podem ser dispositivos com vários limiares; portanto, quando você tem toda a gama de voltagem de limiar sendo usada em um único IP, temos muitos problemas porque cada dispositivo segue em uma direção diferente".

Conclusão

Ainda assim, estão sendo feitos progressos.

“Recentemente, vimos muitas fundições, IDMs, fábricas e empresas de IP correndo para encontrar uma solução”, diz Ramadan. “Eles cobrem uma ampla gama de aplicativos e processos de tecnologia. Enquanto um modelo padrão de envelhecimento pode ser útil como ponto de partida para novos players, novas personalizações são esperadas, dependendo do aplicativo de destino e do processo de tecnologia. A Coalizão de Modelagem Compacta (CMC), sob a

Iniciativa de Integração de Silício (Si2),

atualmente está trabalhando no desenvolvimento de um modelo de envelhecimento padrão para ajudar a indústria. Em 2018, o CMC lançou a primeira Open Model Interface (OMI) padrão que permite a simulação de envelhecimento para diferentes simuladores de circuitos usando a interface OMI padrão unificada. ”

Essa é uma peça importante, mas ainda há um longo caminho pela frente. “As atividades de padronização no CMC começaram a resolver alguns desses problemas”, diz Lange. "Mas há muito trabalho pela frente em termos de complexidade do modelo, esforço de caracterização, cenário de aplicativos e suporte a ferramentas".

@user101 @dayllann