Não.Você usa esses instaladores de driver tipo driver booster? Já vi relatos disso acontecer por causa dos drivers que eles instalam.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

[TÓPICO DEDICADO] AMD Ryzen Socket AM4 - Zen, Zen+, Zen 2 & Zen 3

- Iniciador de Tópicos DemonbrsX

- Data de Início

Essa sua fonte é aquela dinamite da Gigabyte, se vc conseguir arrumar outra, é mais uma coisa a se testar, vai que.

Não é problema com a fonte, esse problema já é antigo. Essa fonte pro meu sistema é bem ok... Se fosse a fonte, não mudaria nada intercalando entre os HDS. O pc nem desliga sozinho.Essa sua fonte é aquela dinamite da Gigabyte, se vc conseguir arrumar outra, é mais uma coisa a se testar, vai que.

Essa sua fonte é aquela dinamite da Gigabyte, se vc conseguir arrumar outra, é mais uma coisa a se testar, vai que.

Gigabomba

GamerNexus explodiu uma com 60% de load.... ridículo.

Passo longe de produtos da gigalixo, nunca mais compro nada dessa marca.Gigabomba

GamerNexus explodiu uma com 60% de load.... ridículo.

Gigabomba

GamerNexus explodiu uma com 60% de load.... ridículo.

Teve um teste na teclab (um mais simples), e a fonte não deu problema. A minha está normal, não está fechando jogos e nem reiniciando o computador. Bem tranquilo tudo em stock. Será substituida futuramente, isso se eu mudar de placa de vídeo.

Parabéns, conseguiram me deixar com medo. Acabei de ver o vídeo do GamerNexus... Jamais uma 3080 encostara nela...

Última edição:

Teve um teste na teclab (um mais simples), e a fonte não deu problema. A minha está normal, não está fechando jogos e nem reiniciando o computador. Bem tranquilo tudo em stock. Será substituida futuramente, isso se eu mudar de placa de vídeo.

Parabéns, conseguiram me deixar com medo. Acabei de ver o vídeo do GamerNexus... Jamais uma 3080 encostara nela...

Tá certo cara, não pode arriscar não...

Imagina uma fonte de menos de 1k estragar uma placa que custa mais de 5 vezes esse valor....

Quero ver se a Gigabyte já corrigiu e está trocando as fontes com defeito de projeto.

Quero ver se a Gigabyte vai ressarcir qualquer dano causado em outros hardwares por essa fonte.

Eu não arrisco nessas marcas de fonte , eu nessa questão sou mais conservador , ou é corsair , superflower etcTá certo cara, não pode arriscar não...

Imagina uma fonte de menos de 1k estragar uma placa que custa mais de 5 vezes esse valor....

Quero ver se a Gigabyte já corrigiu e está trocando as fontes com defeito de projeto.

Quero ver se a Gigabyte vai ressarcir qualquer dano causado em outros hardwares por essa fonte.

ja to com minha HX 620 A 10 ANOS.

Não é necessariamente a Gigabyte que fabrica as fontes, mas, sim, uma OEM chinesa. A GB é totalmente responsável por ter aprovado o projeto falho do modelo P-GM, mas ela também possui modelos muito seguros e confiáveis.Eu não arrisco nessas marcas de fonte , eu nessa questão sou mais conservador , ou é corsair , superflower etc

ja to com minha HX 620 A 10 ANOS.

Sei disso , corsair não fabrica também , superflower fabrica as próprias fontes , corsair andei lendo que as atuais cx/cv teve um corte de orçamento e baixou muito a qualidade , minha hx620 é na real uma seasonic.Não é necessariamente a Gigabyte que fabrica as fontes, mas, sim, uma OEM chinesa. A GB é totalmente responsável por ter aprovado o projeto falho do modelo P-GM, mas ela também possui modelos muito seguros e confiáveis.

CPUs AMD Zen4 Ryzen confirmadas para oferecer gráficos integrados

AMD oferecerá gráficos integrados no chip para a próxima geração da série Ryzen

A próxima geração de CPUs AMD Ryzen agora está confirmada para oferecer GPUs integradas.

AMD Zen4 Ryzen CPUs confirmed to offer integrated graphics - VideoCardz.com

AMD to offer integrated on-chip graphics for next-gen Ryzen series The Next-generation of AMD Ryzen CPUs is now confirmed to offer integrated GPUs. Upcoming Ryzen CPU series based on Zen4 architecture will all offer integrated GPU by design. While this does not mean that literally all CPUs will...

A próxima série de CPU Ryzen baseada na arquitetura Zen4 oferecerá GPU integrada por design. Embora isso não signifique que literalmente todas as CPUs terão iGPUs habilitados, isso confirma que o silício Zen4 mainstream será emparelhado com gráficos pela primeira vez. Assim, a GPU não será mais exclusiva para os APUs Ryzen G-Series.

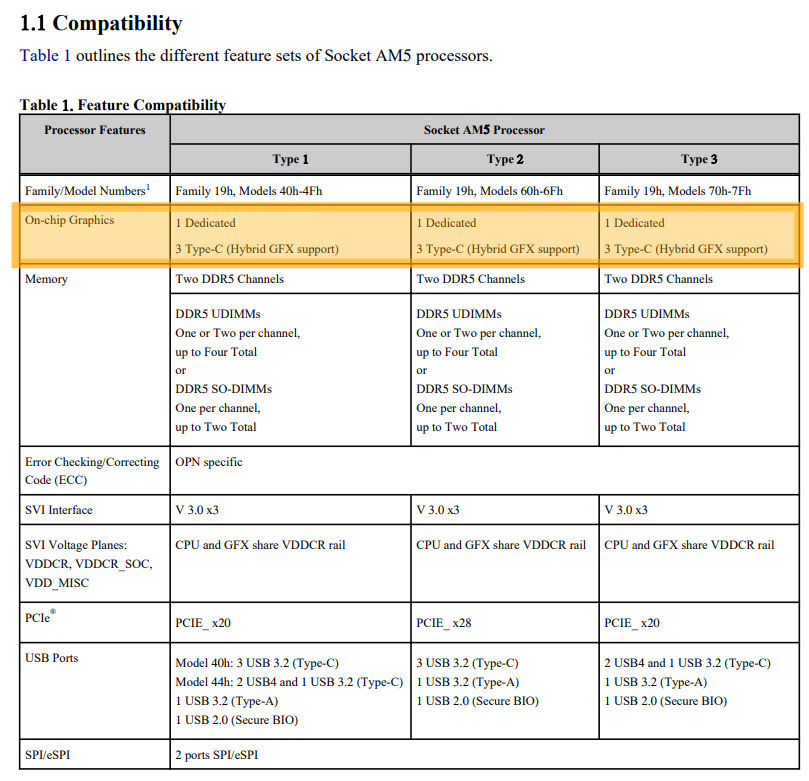

A confirmação chega a partir de documentos vazados que foram obtidos por meio do hack da Gigabyte. Um gráfico de compatibilidade para processadores soquete AM5 foi publicado pela Chips and Cheese . Ele lista três tipos de processadores AM5, todos baseados na microarquitetura Family 19h (Zen4), com gráficos no chip.

O documento afirma que “Alguns OPNs… podem não suportar GFX”. Isso implica que a AMD também venderá CPUs Ryzen com GPU dedicada desabilitada, seja falha de fabricação ou posicionamento do produto, mas essencialmente essas poderiam ser contrapartes da AMD para CPUs 'Intel F-series' que requerem GPU discreta, assim como todos os Zen1-3 não Os processadores Ryzen da série G fazem.

CPUs AMD Família 19H (Zen4) com gráficos no chip, Fonte: Chips and Cheese

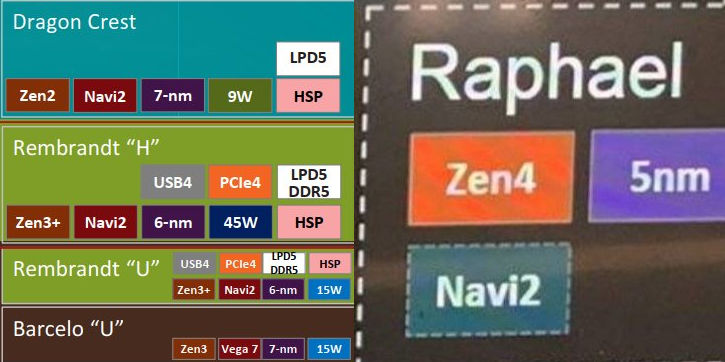

Gráficos integrados AMD Navi2

O roteiro anteriormente vazado listava a microarquitetura gráfica Navi2 (RDNA2) para CPUs Raphael. Este codinome está associado à série de processadores convencionais que deve ser lançada como série Ryzen 7000 no próximo ano. Ao mesmo tempo, a AMD atualizará seus APUs Zen3 com GPU Navi2. Eles serão lançados para o mercado móvel no soquete FP7, mas também podem ser lançados como APUs de desktop (no soquete AM4 ou AM5). O gráfico de compatibilidade postado acima claramente se refere à Família 19H, porém, que implica a microarquitetura Zen4, em outras palavras, não Rembrandt, mas Raphael ou o sucessor de Rembrandt de codinome “ Phoenix ”.

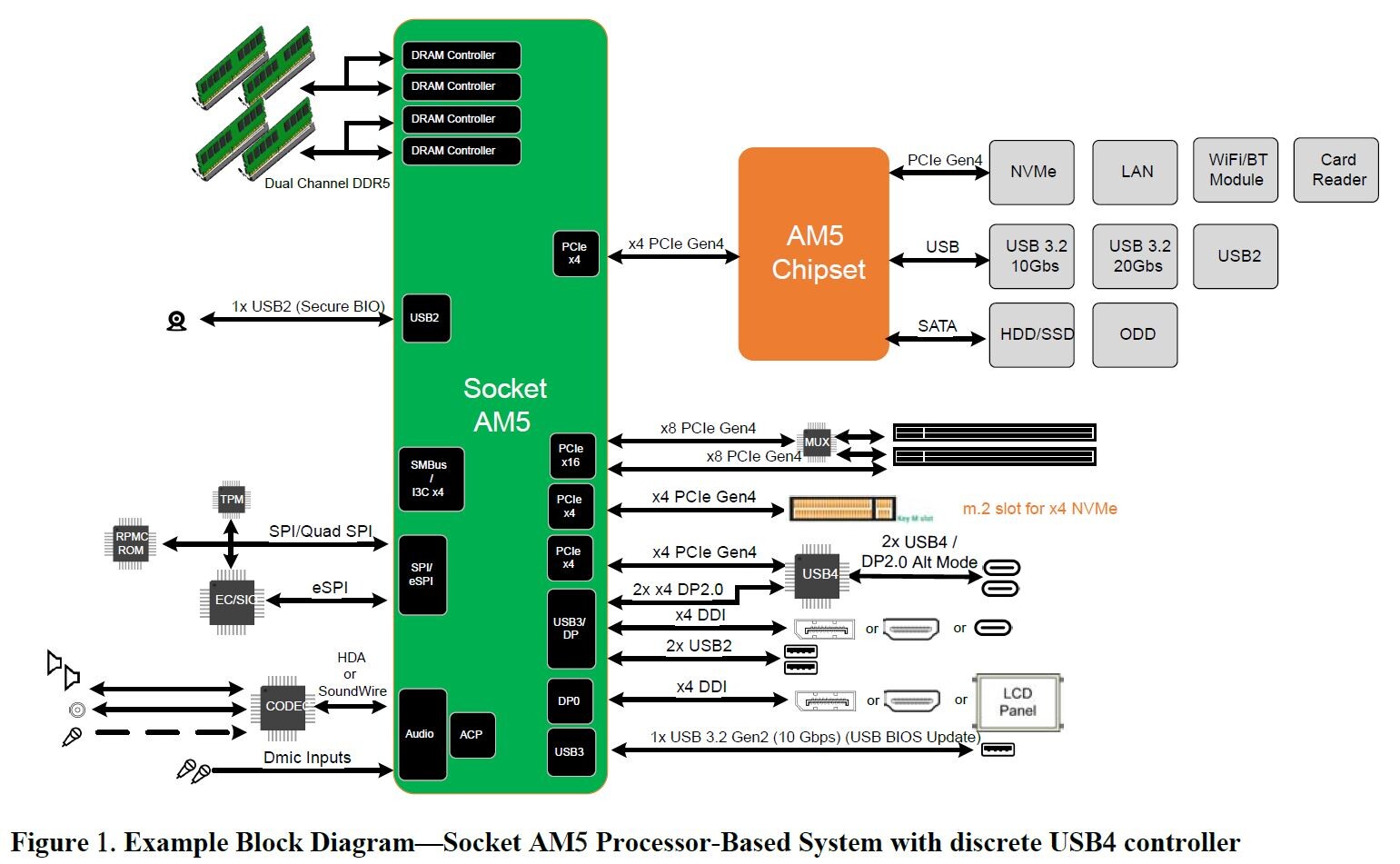

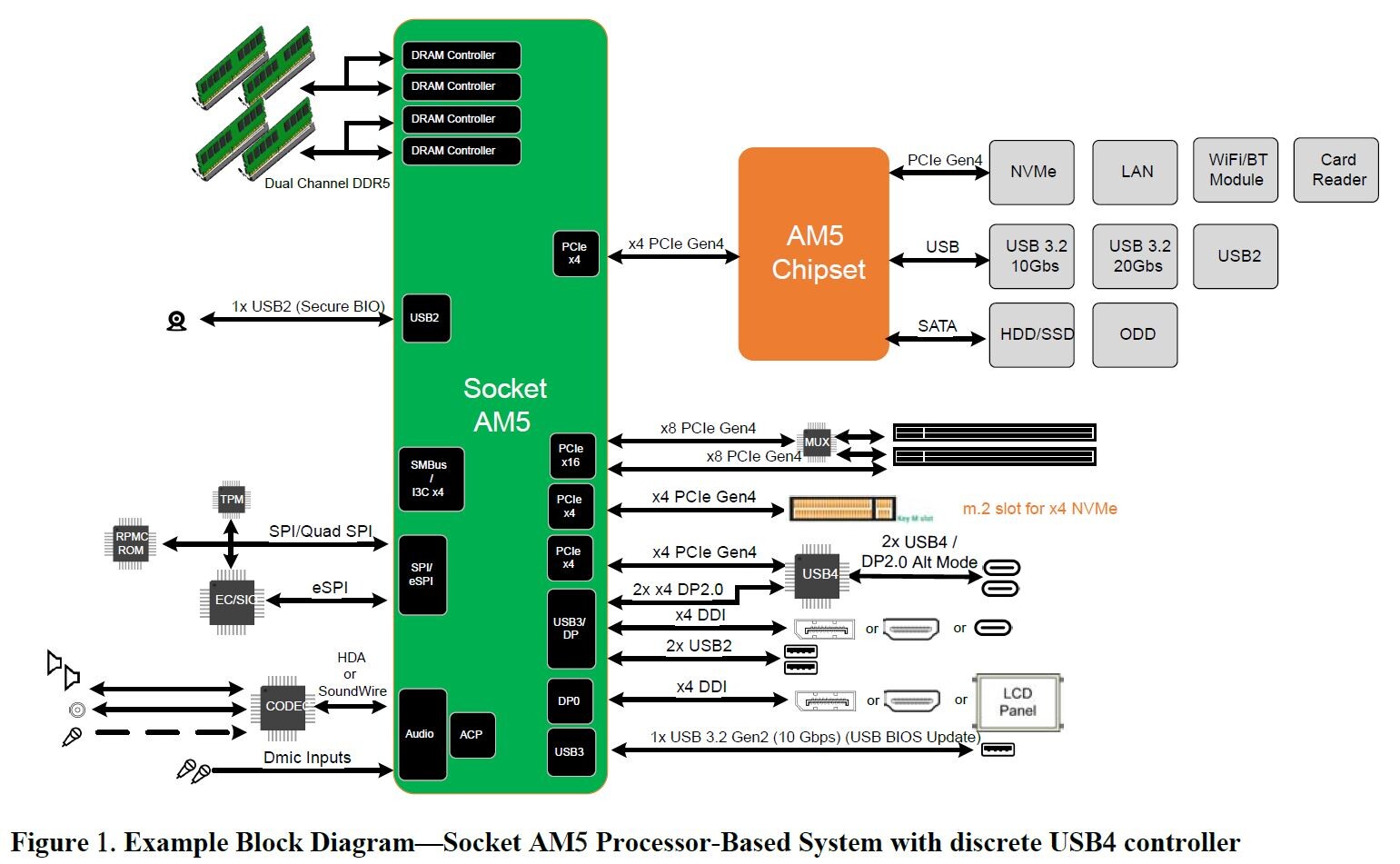

DisplayPort 2.0 não para todas as CPUs?

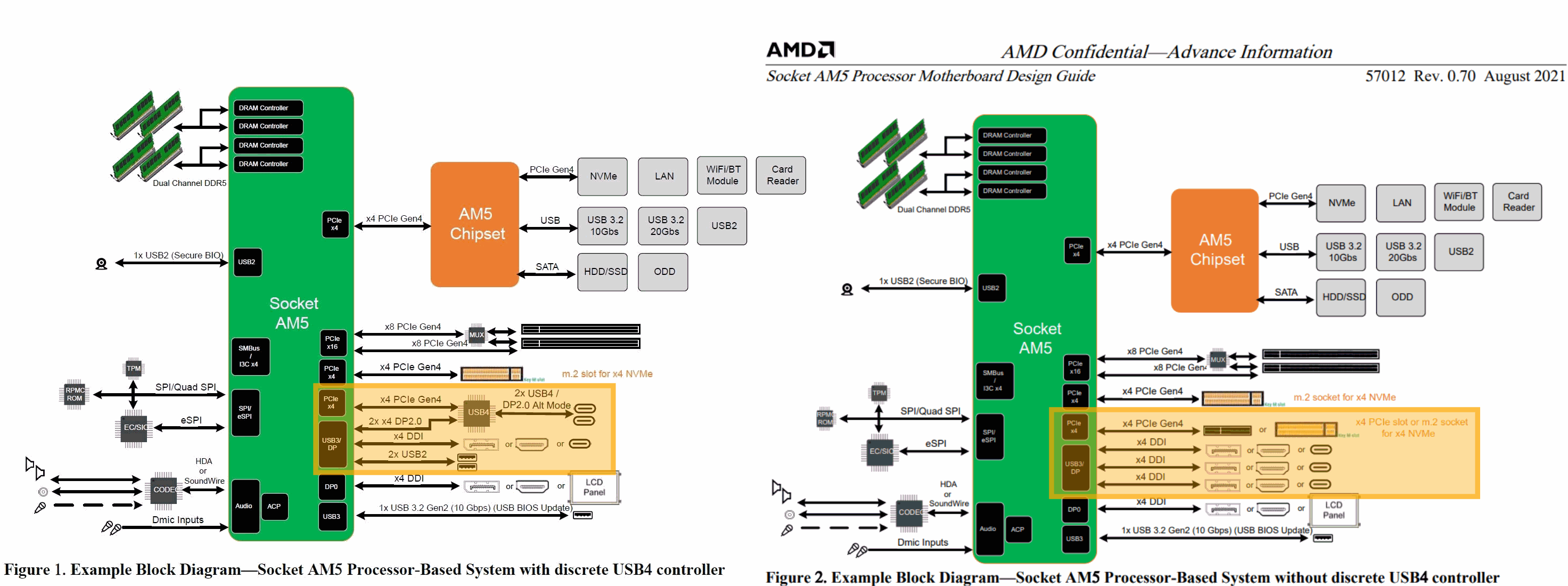

Além disso, Chips and Cheese postou um novo diagrama de blocos demonstrando a plataforma AMD AM5. Este diagrama lista todas as interfaces disponíveis para a CPU e o chipset. Isso confirma, assim como notado no post anterior sobre o vazamento na plataforma, que os processadores soquete AMD AM5 terão mais 4 pistas PCIe Gen4, permitindo mais largura de banda para o drive NVMe secundário ou, alternativamente, dispositivos USB de alta velocidade.

O que é interessante, porém, é que o diagrama C&C recém-compartilhado tem uma pequena diferença quando se trata de listar o DisplayPort 2.0. O diagrama anteriormente vazado listava especificamente “DP2.0”, indicando que as CPUs Ryzen de próxima geração não só terão gráficos integrados, mas também suportarão os padrões de conectividade de tela de última geração, como HDMI 2.1 e DisplayPort 2.0. O diagrama que foi compartilhado por Chips and Cheese não lista DP 2.0, sugerindo que pode ser simplesmente um diagrama para CPUs AMD Zen4 com iGPUs desabilitados.

Plataforma AMD AM5, fonte: TechPowerUP (esquerda), Chips and Cheese (direita)

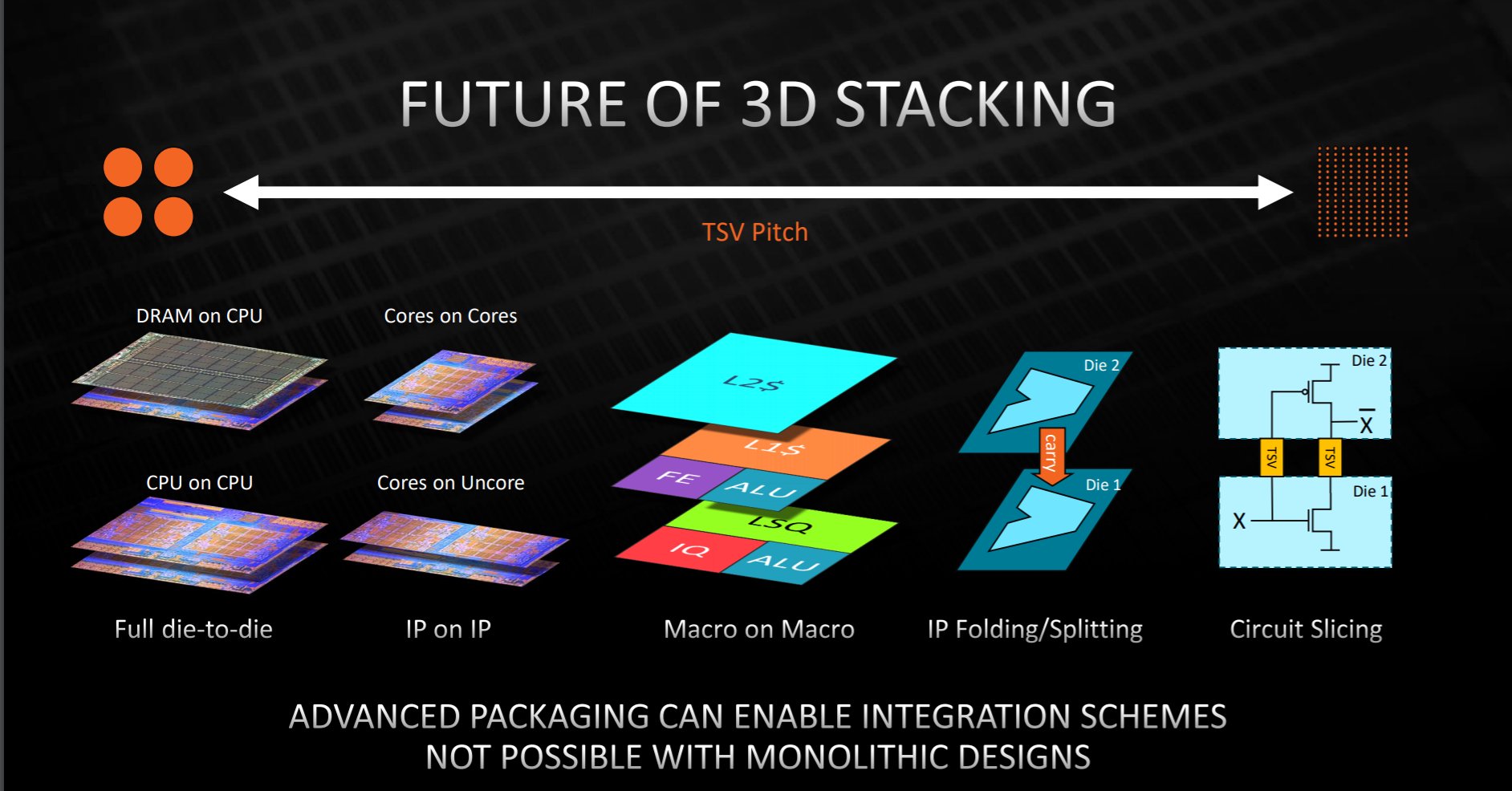

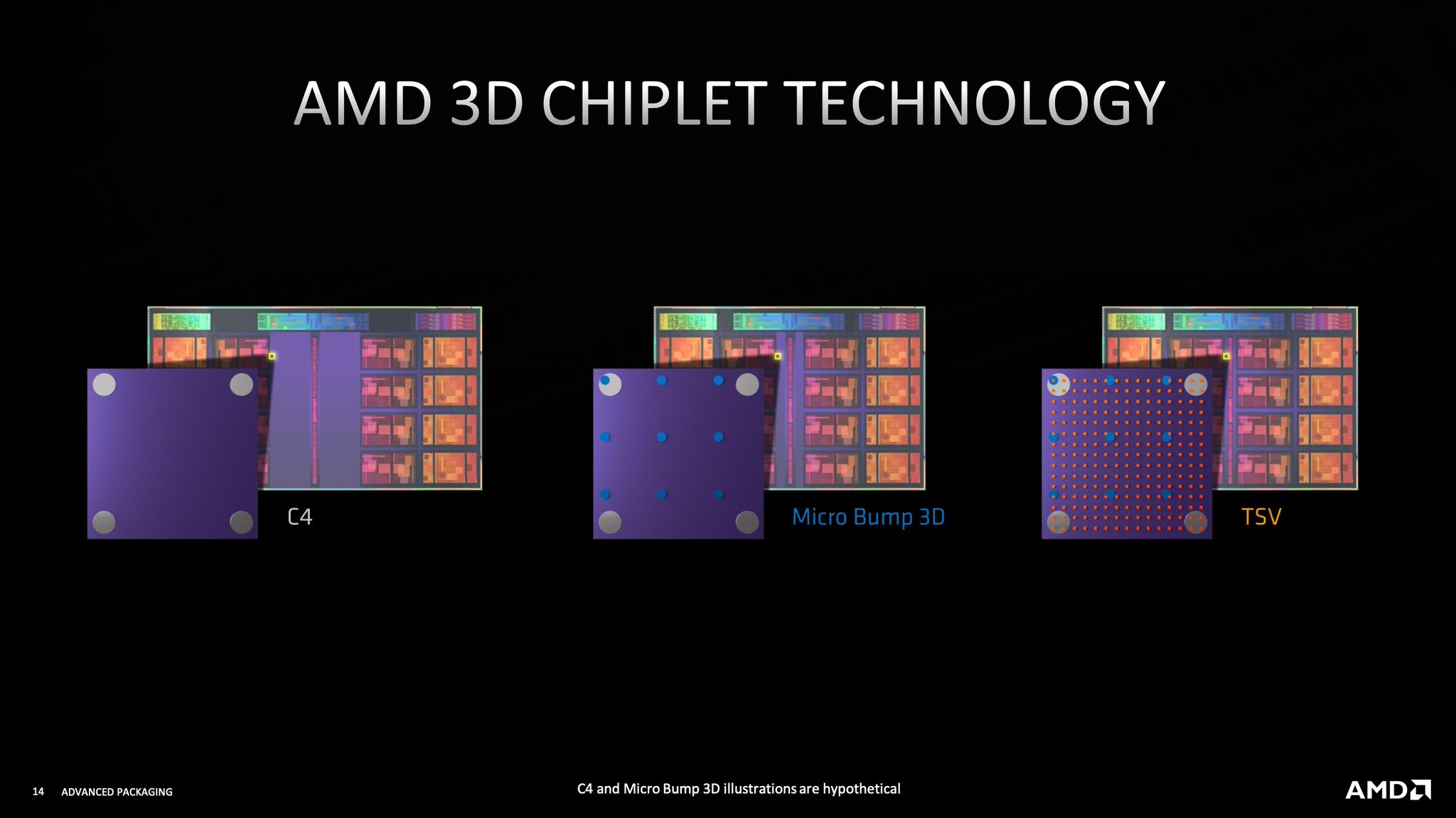

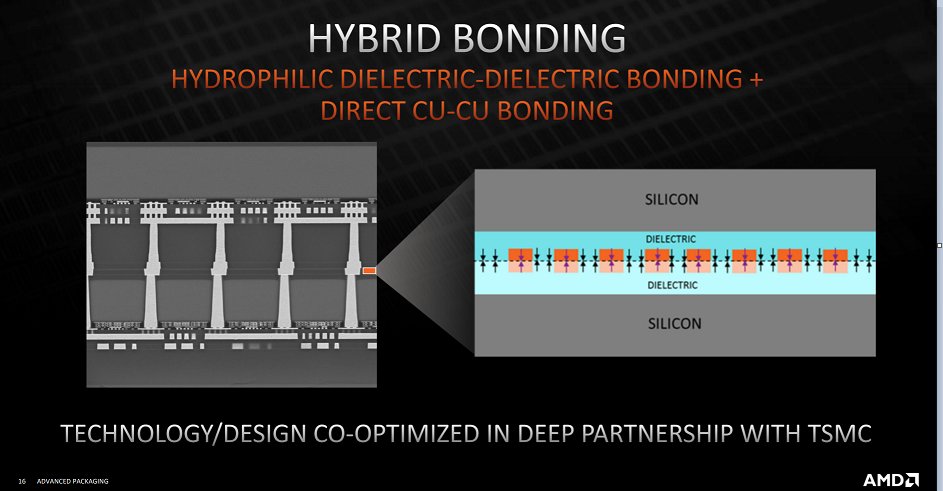

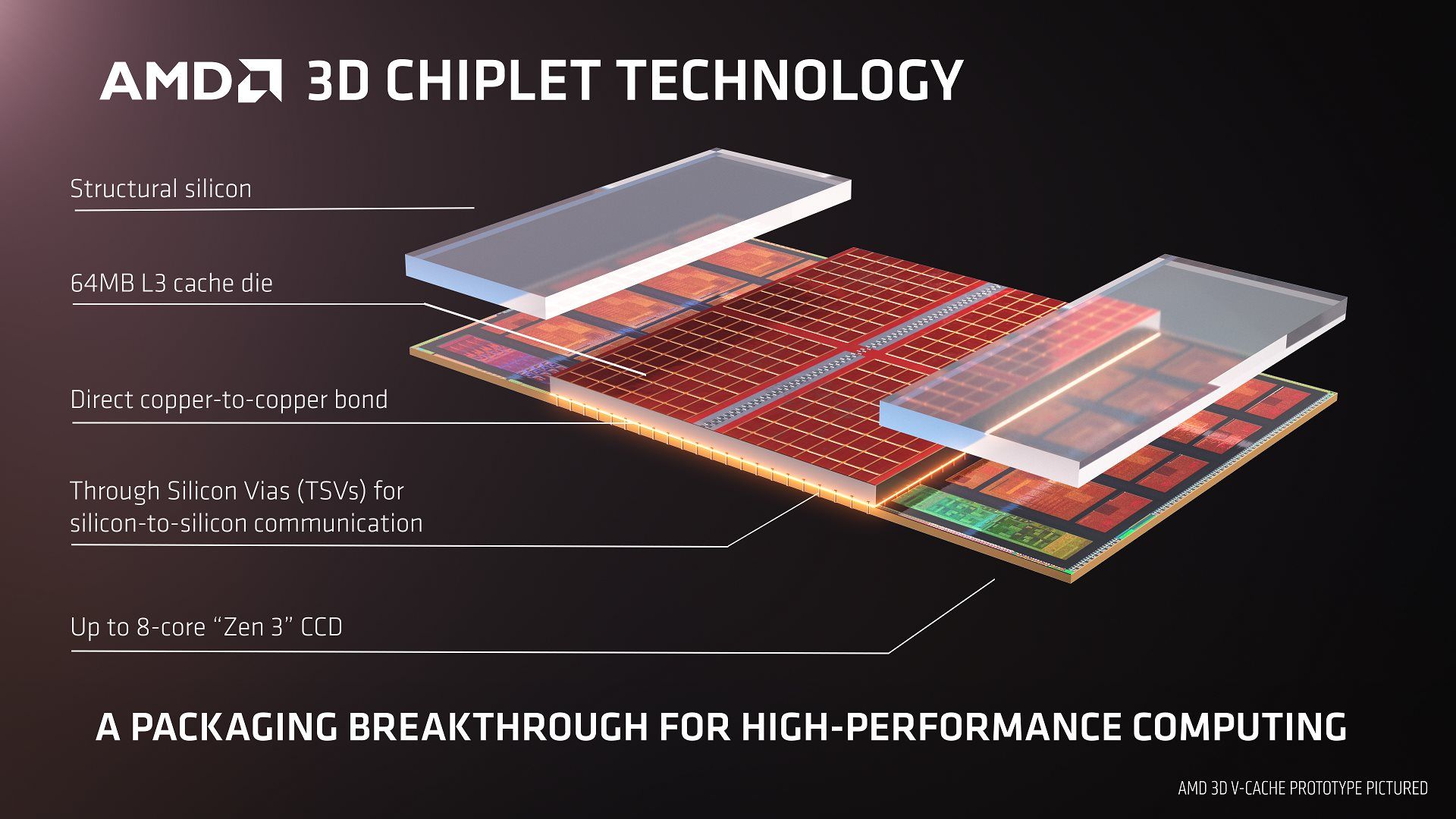

AMD 3D V-Cache usa ligações de pitch de 9 mícrons, o futuro do empilhamento 3D é o corte de circuitos

AMD 3D V-Cache para CPUs Ryzen tem 9 micro pitch bonds

Na apresentação do Hot Chips 33, a AMD descreve o futuro da tecnologia de empilhamento 3D, também compartilhando os primeiros detalhes sobre o empilhamento 3D V-Cache.

AMD 3D V-Cache uses 9 micron pitch bonds, the future of 3D stacking is circuit slicing - VideoCardz.com

AMD 3D V-Cache for Ryzen CPUs has 9 micro pitch bonds In Hot Chips 33 presentation AMD outlines the future of 3D stacking technology, also sharing first details on its 3D V-Cache stacking. AMD presentation showcases existing and future 3D stacking technologies. As the TSV (Through Silicon Via)...

A apresentação da AMD mostra as tecnologias de empilhamento 3D existentes e futuras. Como o TSV (Through Silicon Via), uma inter-wafer vertical ou conexão entre matrizes, vê um aumento nas ligações, a tecnologia se concentrará em designs de empilhamento 3D mais complexos. Neste momento, o empilhamento permite o empilhamento completo de molde a molde, permitindo DRAM em CPUs ou CPUs em CPUs. A tecnologia está progredindo no sentido de colocar módulos separados em si mesmos, como núcleos em núcleos, apenas para permitir que macroblocos sejam empilhados.

Eventualmente, o pitch do TSV será tão denso que a divisão do módulo, dobra ou mesmo a divisão do circuito será possível, o que renovará completamente o futuro dos processadores como os conhecemos hoje. A AMD listou todas as tecnologias de empilhamento existentes, incluindo as técnicas Foveros / EMIB da Intel, sugerindo que a AMD considerou usar esta tecnologia para seus processadores:

A AMD optou por um micro-bump pitch de 9 mícrons, que é um pouco mais denso do que os 10 mícrons do Intel Fovero.

A AMD espera que sua tecnologia 3D Chiplet ofereça eficiência de energia de interconexão 3x maior e densidade de interconexão 15x maior.

O fabricante já havia anunciado seus planos para chipsets 3D baseados no CPU AMD Zen3, apresentando TSV de silício para silício. A tecnologia aumentará o cache do Level3 em 64 MB. A AMD já demonstrou o potencial de sua tecnologia 3D V-Cache na CPU AMD Ryzen 9 5900X com 32 + 64 MB de cache L3. Tal configuração aumenta a taxa de quadros em 15%, revelou a AMD.

De volta à Computex 2021, onde a tecnologia foi mostrada pela primeira vez, a AMD anunciou que as CPUs Ryzen com 3D V-Cache serão produzidas em massa até o final deste ano.

Plataforma AMD AM5 para vazamentos “Raphael” confirmando suporte PCIe Gen4, memória DDR5 de canal duplo

O diagrama de blocos do chipset AMD série 600 para processadores soquete AM5 vazou

TechPowerUP tem uma imagem da plataforma de soquete AMD AM5 que confirma o suporte a PCIe Gen4.

AMD AM5 platform for "Raphael" leaks confirming PCIe Gen4 support, dual channel DDR5 memory - VideoCardz.com

Block diagram of AMD 600-series chipset for AM5 socket CPUs has leaked TechPowerUP has a picture of the AMD AM5 socket platform which confirms PCIe Gen4 support. Yesterday Intel confirmed its upcoming 12th Gen Core Series codenamed “Alder Lake” will be the first to support PCIe Gen5. Meanwhile...

Ontem a Intel confirmou que sua próxima Série Núcleo da 12ª Geração codinome “Alder Lake” será a primeira a oferecer suporte a PCIe Gen5. Enquanto isso, a série de CPU Raphael Ryzen da AMD, que agora é esperada para 2022, não suportará este padrão, confirma um diagrama que vazou. A origem deste diagrama é provavelmente do hack Gigabyte / AMD, o TechPowerUP parece ter obtido acesso a esses arquivos.

O chipset AMD AM5 deve oferecer 16 + 4 + 4 pistas PCIe Gen4, garantindo que gráficos de ponta, drive NVMe de alta velocidade e dispositivos USB4 possam ser conectados simultaneamente. Além disso, o chipset AM5 da série 600 oferecerá 4 pistas.

As CPUs AMD AM5 devem suportar memória DDR5 de canal duplo. Este diagrama específico não indica a velocidade máxima da memória com suporte.

O diagrama confirma que a plataforma AMD AM5 suportará DisplayPort 2.0, que é conectado a 4 pistas PCIe Gen4 adicionais por meio de um controlador USB versão 4.

A série AMD Ryzen 7000 codinome Raphael deve apresentar a microarquitetura Zen4 a bordo. As configurações das CPUs ainda não são conhecidas, mas os documentos aparentemente confirmam que a série tem RDNA2 GPU integrado, um recurso que estava faltando em todas as séries anteriores de CPU Ryzen (não deve ser confundido com APUs).

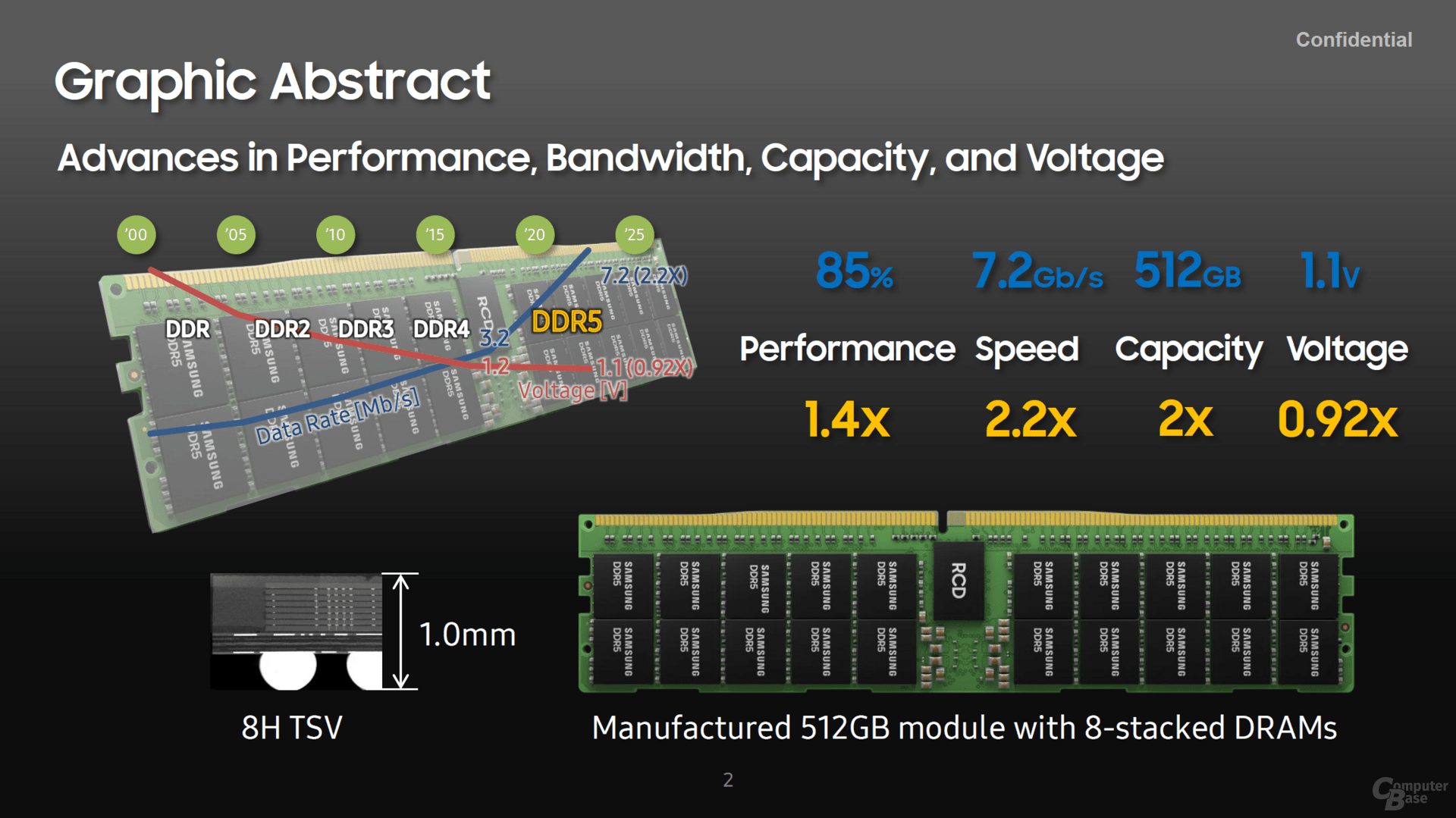

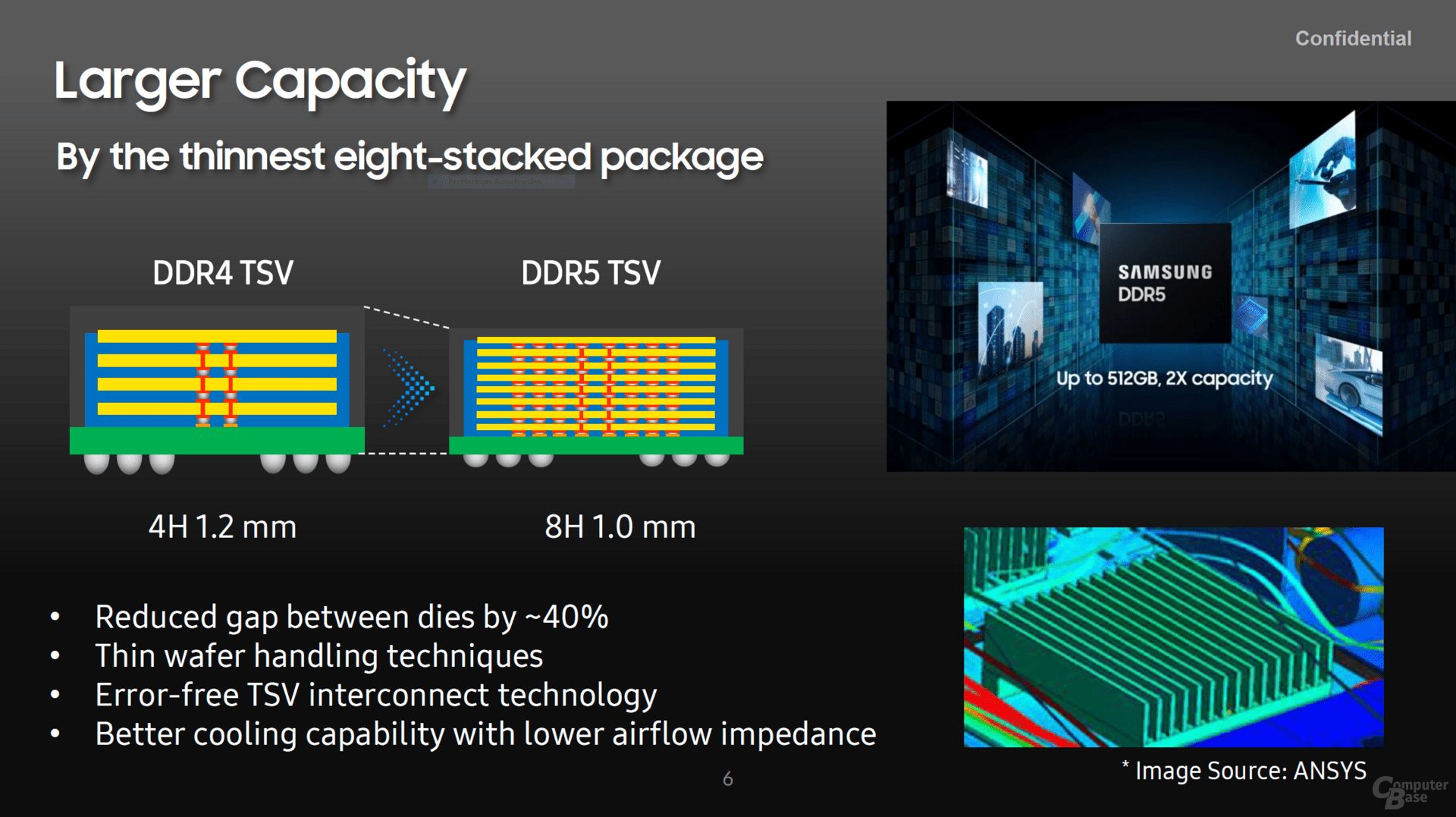

A Samsung planeja módulos de memória TSV DDR5 de 8 empilhados com capacidade total de até 512 GB

Samsung revela metas para memória DDR5: módulos TSV de 8 pilhas

Na HotChips 33, a Samsung confirmou que está desenvolvendo um módulo de memória DDR5 com módulos TSV de 8 pilhas, o dobro do que a memória DDR4 era capaz. Isso significa que teoricamente, módulos de memória de 512 GB são possíveis no futuro.

Samsung plans 8-stacked TSV DDR5 memory modules with up to 512GB total capacity - VideoCardz.com

Samsung unveils goals for DDR5 memory: 8-stack TSV modules At HotChips 33 Samsung confirmed it is developing a DDR5 memory module featuring 8-stacks TSV modules, a double of what DDR4 memory was capable of. This means that theoretically, 512GB memory modules are possible in the future. With...

Com embalagem otimizada, a Samsung planeja trazer embalagens de oito pilhas com alturas menores do que a memória DDR4 de 4 pilhas. A redução da altura foi possível graças a um menor intervalo entre as matrizes (redução de 40%) e pela implementação de técnicas de manuseio de wafer fino. É importante ressaltar que os módulos TSV de 8 pilhas oferecem melhores recursos de resfriamento.

Um módulo DDR5 de 8 pilhas habilitará capacidades de até 512 GB por módulo. Este é um grande aumento em comparação com a memória DDR4, que oferece principalmente capacidades de 32 e 64 GB no máximo, com um fornecimento limitado de módulos de 128 GB ou 256 GB para o mercado de servidores.

A Samsung espera que a memória DDR5 forneça até 85% de aumento de desempenho em relação à DDR4, largura de banda de até 7,2 Gbp / s e capacidade dobrada de até 512 GB. Ao mesmo tempo, os novos módulos apresentarão uma tensão inferior de 1,1 V, que em conjunto com a regulação de tensão do módulo aumentará a eficiência energética. Os módulos RDIMM / LRDIMM de 512 GB anunciados são, obviamente, para o mercado de data center. Os consumidores não devem esperar capacidades além do UDIMM de 64 GB tão cedo.

De acordo com a Samsung, o crossover do mercado principal para DDR5 não deve ser esperado até 2023/2024. A transformação para o mercado de data center deve acontecer mais cedo, por isso a Samsung planeja fabricar módulos DDR5-7200 de 512 GB até o final deste ano.

Tenho uma TUF B550M Plus com 3800XT, e SN550 e SN750 Heatsink. Atualizei ontem a BIOS para a versão mais recente no site da Asus, já que estava dando (e continua a dar) um problema com a Webcam da Ryzen quando conectada na porta USB 3.2. Nada foi resolvido sobre o problema no USB, mas agora o SSD SN750 passou a marcar uns 5 graus a mais na temperatura. Resetei a BIOS, e ficou tudo da mesma forma. Será que é normal isso?

Tão fazendo muito drama da intel vir com PCI-E 5.0 e AMD não , a real que isso vai encarecer ainda mais a plataforma , no caso da intel pelo que vi não será utilizando nos slots m2 terá apenas em um slot PCIE X16 5.0 ,inicialmente mais funcionar de mkt do que realmente funcional , provavelmente AMD vai implantar no zen 5 apenas quando produtos pcie 5.0 fizerem algum sentido com uma solução mais completa , slots m2 e pcie, similar como foi feito no PCIE4.0 .

Pro mercado mainstream acho bem inútil tb, não vai fazer diferença alguma. Porém pro mercado de servidores e até um pouco do HEDT isso é super relevante, e se a AMD ficar pra trás (nem que sejam 3~4 meses) sem PCIe 5.0 implica em empresas começarem validações de plataforma somente com Intel, da mesma forma que foi o PCIe 4.0 somente com plataformas AMD.Tão fazendo muito drama da intel vir com PCI-E 5.0 e AMD não , a real que isso vai encarecer ainda mais a plataforma , no caso da intel pelo que vi não será utilizando nos slots m2 terá apenas em um slot PCIE X16 5.0 ,inicialmente mais funcionar de mkt do que realmente funcional , provavelmente AMD vai implantar no zen 5 apenas quando produtos pcie 5.0 fizerem algum sentido com uma solução mais completa , slots m2 e pcie, similar como foi feito no PCIE4.0 .

Epyc genoa terá suporte a PCIE 5.0 provavelmente nova gen threadripper tambem ira receberPro mercado mainstream acho bem inútil tb, não vai fazer diferença alguma. Porém pro mercado de servidores e até um pouco do HEDT isso é super relevante, e se a AMD ficar pra trás (nem que sejam 3~4 meses) sem PCIe 5.0 implica em empresas começarem validações de plataforma somente com Intel, da mesma forma que foi o PCIe 4.0 somente com plataformas AMD.

Tão fazendo muito drama da intel vir com PCI-E 5.0 e AMD não , a real que isso vai encarecer ainda mais a plataforma , no caso da intel pelo que vi não será utilizando nos slots m2 terá apenas em um slot PCIE X16 5.0 ,inicialmente mais funcionar de mkt do que realmente funcional , provavelmente AMD vai implantar no zen 5 apenas quando produtos pcie 5.0 fizerem algum sentido com uma solução mais completa , slots m2 e pcie, similar como foi feito no PCIE4.0 .

Se não vier em m.2 aí é sacanage, melhor quando implementar em tudo de uma vez. Se não vai ter que fazer up da mobo hueheuhuehu

Esse é o famoso bug nas usbs que não funcionam? Pode me explicar melhor o que ocorre, não funciona nada nessa usb ou alguns dispositivos?Tenho uma TUF B550M Plus com 3800XT, e SN550 e SN750 Heatsink. Atualizei ontem a BIOS para a versão mais recente no site da Asus, já que estava dando (e continua a dar) um problema com a Webcam da Ryzen quando conectada na porta USB 3.2. Nada foi resolvido sobre o problema no USB, mas agora o SSD SN750 passou a marcar uns 5 graus a mais na temperatura. Resetei a BIOS, e ficou tudo da mesma forma. Será que é normal isso?

Tão fazendo muito drama da intel vir com PCI-E 5.0 e AMD não , a real que isso vai encarecer ainda mais a plataforma , no caso da intel pelo que vi não será utilizando nos slots m2 terá apenas em um slot PCIE X16 5.0 ,inicialmente mais funcionar de mkt do que realmente funcional , provavelmente AMD vai implantar no zen 5 apenas quando produtos pcie 5.0 fizerem algum sentido com uma solução mais completa , slots m2 e pcie, similar como foi feito no PCIE4.0 .

Cara, AMD trazer PCI-E 4.0 em 2019 foi inútil.

Acho que a AMD acertou em deixar PCI-E 5.0 para 2022.

Pelo diagrama do chip7 será somente no slot pcie mesmo, os slots m2 será gen 4 e dependendo da mobo com gen 3 tambem .Se não vier em m.2 aí é sacanage, melhor quando implementar em tudo de uma vez. Se não vai ter que fazer up da mobo hueheuhuehu

Cara, AMD trazer PCI-E 4.0 em 2019 foi inútil.

Acho que a AMD acertou em deixar PCI-E 5.0 para 2022.

inútil não foi, arquitetura que trouxe ou pcie 4 é a mesma dos consoles com SSDs rápidos e o futuro direct storage, foi necessário, e principalmente na linha Epyc / TR que faz o uso dessa banda toda.

inútil não foi, arquitetura que trouxe ou pcie 4 é a mesma dos consoles com SSDs rápidos e o futuro direct storage, foi necessário, e principalmente na linha Epyc / TR que faz o uso dessa banda toda.

PCI express 4.0 só fez diferença em 2020. Nvme 7.000MB/s+, placas de vídeo pci express 4.0....

Em 2019 só tinha nvme "de entrada" tirando proveito (5.000MB/s).

PCI express 4.0 só fez diferença em 2020. Nvme 7.000MB/s+, placas de vídeo pci express 4.0....

Em 2019 só tinha nvme "de entrada" tirando proveito (5.000MB/s).

Mas sem PCIe 4.0, os consoles não iriam ter a tecnologia que tem, pois dependiam da AMD, é isso que estou falando, lançamento do Windows 11 + Direct Storage, vai começar a fazer bom uso dele.

Quanto ao bug do USB, não sei dizer com certeza. Mas é fato que quando eu conecto a Razer Kiyo Pro na porta USB 3.2 dá erro de leitura e o sistema fica lento ao ponto de quase travar. E não é problema do sistema operacional, pois dá o mesmo problema no Arch e no Windows.Esse é o famoso bug nas usbs que não funcionam? Pode me explicar melhor o que ocorre, não funciona nada nessa usb ou alguns dispositivos?

Tem algum log relevante no journalctl e/ou no dmesg?Quanto ao bug do USB, não sei dizer com certeza. Mas é fato que quando eu conecto a Razer Kiyo Pro na porta USB 3.2 dá erro de leitura e o sistema fica lento ao ponto de quase travar. E não é problema do sistema operacional, pois dá o mesmo problema no Arch e no Windows.

Users who are viewing this thread

Total: 5 (membros: 0, visitantes: 5)