Pra 1440p o 3700X dá e sobra. Jogo nessa resolução aqui e o 3700X sobra com folgas. Pra essa resolução a diferença maior vai ser na VGA.Estou no mesmo dilema aqui, tenho um 3700x em uma X470 Gaming 7, RTX 2080 e 32GB 3600, estou esperando a poeira baixar um pouco pra pegar uma 3070TI, mas queria trocar meu CPU também por um 5800x, jogo em Quad HD, não sei se realmente vale a pena gastar quase 3k em um novo CPU.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

[TÓPICO DEDICADO] AMD Ryzen Socket AM4 - Zen, Zen+, Zen 2 & Zen 3

- Iniciador de Tópicos DemonbrsX

- Data de Início

A diferença da estratégia da INTEL (EMIB - Embedded Multi-Die Interconnect Bridge / Foveros)

vs

AMD (MCMs ou Módulos Multi-Chip)

O 3D V-Cache da AMD assume a liderança em pacotes avançados

AMD’s 3D V-Cache takes the advanced packaging lead

AMD just vaulted back into the advanced packaging lead last night with their 3D V-Cache technology.

semiaccurate.com

semiaccurate.com

AMD Confirms Zen 3 Ryzen CPUs With 3D V-Cache Stack Chiplet Design, Coming Early Next Year Before Zen 4

AMD has confirmed that the 3D V-Cache stack chiplet technology will be introduced in its Zen 3 powered Ryzen CPUs coming early next year.

A AMD acabou de voltar à liderança em embalagens avançadas ontem à noite com sua tecnologia 3D V-Cache. SemiAccurate tentará explicar por que isso está muito além do que outros fizeram ou mesmo mostraram.

Mostre-me o dinheiro do cache!

Aula de História:

A AMD é frequentemente considerada a primeira no mercado de massa com um produto de embalagem 2.5D em sua GPU Fiji em 2015 . Ele usa memória HBM em um mediador passivo de silício, basicamente uma CPU gigante sem transistores. Pode estar pegando lêndeas, mas a Xilinx chegou lá vários anos antes com seus grandes FPGAs Virtex, mas eles têm um preço ligeiramente diferente. A mensagem para levar para casa aqui é que o silício em embalagens de silício já existe há um tempo e a AMD é a líder absoluta na fabricação de dispositivos de volume 2.5D com preços de mercado de massa. Ninguém mais fez isso de forma consistente e econômica.

Passando para uma tecnologia menos avançada, a AMD foi para MCMs ou Módulos Multi-Chip em 2017 com Nápoles e depois para chips em 2019 com Roma, ambos produtos de servidor que venderam dezenas de milhões de dispositivos. Do lado do consumidor, os grandes Ryzens da geração Roma também usaram a mesma tecnologia e venderam uma ordem de magnitude a mais de chips.

O problema com os MCMs e os chips é que eles são tecnologia antiga, os MCMs existem desde o início dos tempos e são antigos. A AMD os usou com eficácia devastadora no mercado, mas isso foi devido ao planejamento inteligente e à visão geral, o pensamento clássico fora da caixa. Eles usaram bem as ferramentas que possuíam, em vez de fazer algo tecnicamente novo. Embora você possa argumentar que os chips em Roma são uma ideia nova, é um exagero.

Concorrência:

Mindshare no mundo do empacotamento avançado foi sugado pela Intel recentemente com suas duas tecnologias líderes, Foveros e EMIB. Ambos são realmente interessantes, eficazes e provavelmente não fazem o que você pensa que fazem. Tampouco são a tecnologia matadora que lançará qualquer competidor no mato, mas eles são sólidos se usados apropriadamente. A chave aqui é o escopo e quão grande alguns querem que você pense que é.

EMIB significa Embedded Multi-Die Interconnect Bridge e é bastante único. Se você olhar para Fiji da AMD no link acima, verá que o interposer é enorme, é maior do que a pegada das stacks de GPU e HBM mais todos os espaços em branco. Silício desse tamanho, mesmo em um processo antigo com apenas algumas camadas de metal, não é barato, nem a montagem. Como o silício sobre o silício significa baixa ou nenhuma incompatibilidade de expansão térmica que diminui o rendimento e destrói os chips, ele tende a ser uma maneira inteligente de projetar as coisas.

A ideia por trás do EMIB é pegar uma fatia fina de material intermediário, basicamente um fio feito de um chip, e embuti-lo no PCB orgânico verde padrão no qual uma CPU ou MCM é normalmente montada. O custo do pacote aumenta um pouco e a montagem fica um pouco mais complicada, mas o custo do 'intermediário' diminui. Resumindo, você só paga pelo mediador onde precisa e em nenhum outro lugar. Em teoria, é um caminho muito melhor.

O problema aqui é que você tem incompatibilidades de expansão térmica entre os materiais orgânicos e o silício que os intermediários evitam. Este é provavelmente um problema menor de custo e rendimento, que a Intel provavelmente resolveu por meio de uma engenharia cuidadosa. Outro problema é o alinhamento, é mais difícil montar matrizes em substratos incompatíveis, mas, novamente, esse é um problema que a Intel parece ter resolvido.

Um problema que é mais fundamental para o EMIB são os pacotes de vários saltos, basicamente um dispositivo que tem uma estrutura de matriz <-> EMIB <-> matriz <-> EMIB <-> matriz. Cada link tem margens de erro e eles se somam a cada salto, erros aditivos tornam-se dolorosos muito rapidamente. Até agora a Intel falou apenas sobre um único produto, o Stratix 10 GX 10M FPGA , que usa uma configuração multi-hop altamente complexa. Desde o 'lançamento' de 2019, a SemiAccurate não viu nenhuma imagem de silício funcionando nem está à venda, pelo que sabemos. Sim, existem páginas da web sobre isso, mas nossas fontes no mundo FPGA não conseguiram encontrar nenhuma.

EMIB é a melhor maneira em teoria. No mundo real, dependendo da complexidade do dispositivo, pode ser a melhor maneira também. Quanto mais complexo for o dispositivo, mais perdas de rendimento e montagem você terá e em algum ponto ao longo do caminho você cruzará o ponto onde os intermediários são mais baratos e eficazes. Esse ponto provavelmente muda a cada novo dispositivo, então o que era certo na semana passada pode não ser hoje. A mensagem para levar para casa aqui é que o EMIB não é o aplicativo matador, é útil, mas não é um kill limpo de forma alguma.

Foveros:

Foveros é o outro tambor que a Intel vem batendo em embalagens avançadas, e com bons motivos. Ele foi exibido pela primeira vez no final de 2018 em um protótipo Lakefield SoC . Dito isso, esqueça o chip por enquanto, vamos dar uma olhada na construção. Foveros é o nome da Intel para a tecnologia de embalagem face a face (F2F) e é impressionante. Em vez de usar TSVs (através de Silicon Vias) para embalagens 3D, Foveros apenas vira um dado e o une ao que está abaixo. Isso significa que é mais barato fazer, você perde menos área para os TSVs e evita as perdas de rendimento ao fazer milhares de furos em sua matriz.

A desvantagem é que com Foveros você só pode empilhar duas matrizes, com TSVs você pode, teoricamente, ir tão alto quanto quiser. Foveros também evita os problemas de erro aditivo de stacks de dies múltiplas, então os rendimentos devem ser maiores, ou pelo menos as mitigações de perda de montagem serão menos onerosas. O preço por esta simplicidade é obviamente a falta de escala, mas por outro lado é um ótimo caminho a percorrer.

A energia é o grande problema com o Foveros, ao colocar um dado ativo em um dado ativo você está colocando duas fontes de calor, os transistores, entre dois isoladores, o silício. Normalmente, grande parte do calor de um chip é extraído das camadas de metal e dos pinos, algo muito mais difícil de fazer em um dispositivo F2F. É por isso que a Intel só mostrou dispositivos de baixo consumo de energia usando Foveros.

Em geral, a Foveros funciona e a Lakefield já está embarcando há mais de um ano, mas em volumes muito baixos. Isso aponta para alto custo e baixo rendimento, algo que não inspira confiança de que os rolamentos Foveros serão adequados para os volumes de consumo. Mais uma vez este é um desafio de engenharia que pode ser superado, basta perceber que com o que foi mostrado até agora, ainda é uma questão em aberto.

Poder Poder Poder:

Montagem, rendimento e custo são grandes problemas com essas tecnologias avançadas, mas todos são problemas de engenharia que podem e, em sua maioria, foram superados ao longo dos anos. O poder e o calor que o acompanha é algo que ainda não foi superado, pelo menos na medida em que alguns gostariam que você acreditasse. Os dispositivos intermediários e chips da AMD têm suas matrizes de silício de alta potência espalhadas na embalagem. A desastrosa primeira tentativa da Nvidia de intermediários e da HBM teve rendimentos mais baixos do que até mesmo o primeiro Fermi devido à falta de noções básicas de engenharia.

O EMIB e o Foveros da Intel têm um monte de relações públicas por trás deles e existem produtos reais no mercado também. Todos são mais uma prova de conceito de baixo volume do que produtos de mercado de massa, nenhum deles chega perto dos produtos de embalagem avançada da AMD de menor volume. Dito isso, todos eles são de menor potência ou usam matrizes espalhadas no caso do EMIB. Até o momento, ninguém lançou um produto de alta potência que não use chips espalhados, não importa a tecnologia. A maioria vai falar e entoar que não é um problema, especialmente para o ouvinte menos técnico, mas a tecnologia ainda não está lá para fazer produtos reais.

Digite AMD novamente:

Isso nos leva de volta à AMD e seu discurso principal Computex 2021. Resumindo, a AMD simplesmente chutou todos os outros concorrentes com sua tecnologia, mesmo que eles não a mencionassem explicitamente. O que eles fizeram foi uma virada de jogo, mas não o Santo Graal da tecnologia de embalagem avançada. Pense nisso como um grande passo que renderá dividendos significativos no mercado. Mais uma vez, ninguém mostrou nada parecido e a AMD está planejando iniciar a produção de volume para o consumidor este ano.

Melhor então se concentrar no Upgrade da VGA, mas os preços estão fora da realidade, quando tudo voltar ao normal penso nisso então.Pra 1440p o 3700X dá e sobra. Jogo nessa resolução aqui e o 3700X sobra com folgas. Pra essa resolução a diferença maior vai ser na VGA.

Valeu pela força.

Asus B550-F ou X570 Tuf pra levar um 5600x?

Tanto faz, depende das features que vc vai querer, ambas seguram o 5600x com OC com um pé nas costas.Asus B550-F ou X570 Tuf pra levar um 5600x?

Tanto faz, depende das features que vc vai querer, ambas seguram o 5600x com OC com um pé nas costas.

Asus B450m pro gamming segura over com o 5600x?

Amigos meu 2700 morreu, visando uso principalmente em edição de vídeos, qual substituto seria ideal? 3700x 3800xt ou 5800x? Lembrando que uso uma b450 tomahalk, pretendo pegar no aliexpress, amd deve oferecer reembolso do valor da nota fiscal mais correção, não queria completar muito mais grana além (deve ficar em 1200.00 visto que paguei 850 nele em 2019)

Edição de vídeos: 3900X melhor que 5800X.Amigos meu 2700 morreu, visando uso principalmente em edição de vídeos, qual substituto seria ideal? 3700x 3800xt ou 5800x? Lembrando que uso uma b450 tomahalk, pretendo pegar no aliexpress, amd deve oferecer reembolso do valor da nota fiscal mais correção, não queria completar muito mais grana além (deve ficar em 1200.00 visto que paguei 850 nele em 2019)

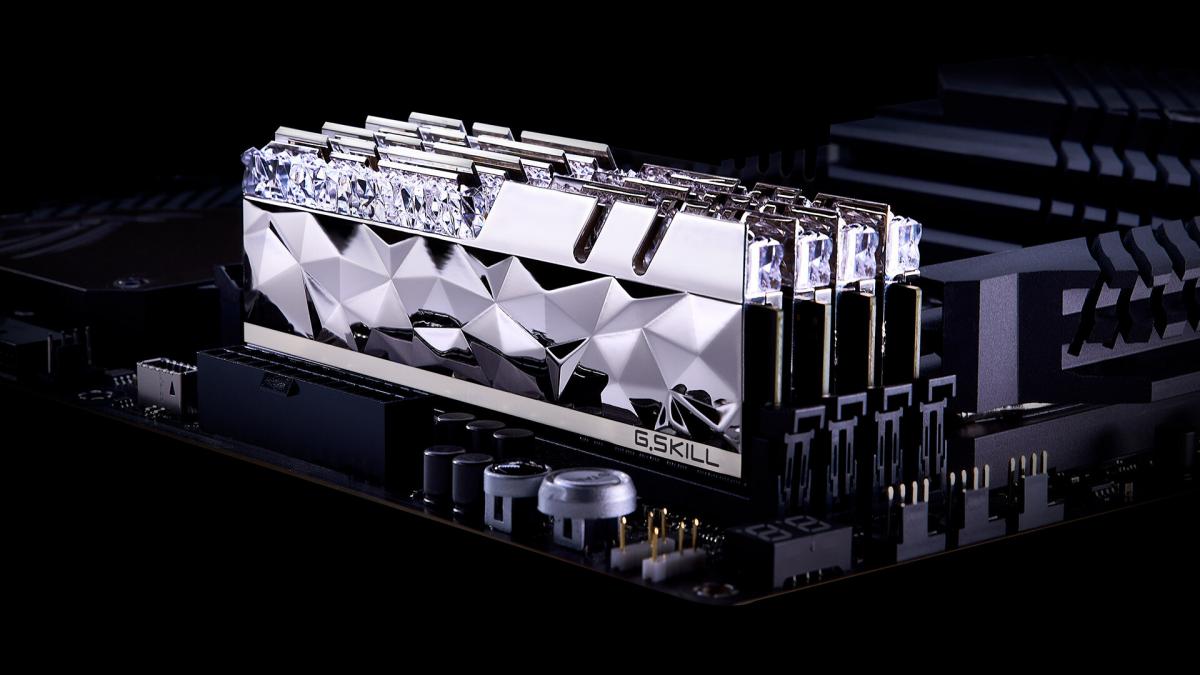

G.,Skill offers Trident Z Royal Elite Performance CL14 Low-Latency Kits Up To DDR4-4000 32GB

G.SKILL is thrilled to announce the availability of the latest Trident Z Royal Elite memory series, along with the introduction of new high-speed, low-latency performance memory specifications at DDR4...

meu deus que memórias, quero uma dessas, vai casar maravilhosamente com os ryzen

Tô ligado mano, problema é o Cash kk, 3500,00 num 3900x é fora pra mim. Mas é god esse.Edição de vídeos: 3900X melhor que 5800X.

Amigos meu 2700 morreu, visando uso principalmente em edição de vídeos, qual substituto seria ideal? 3700x 3800xt ou 5800x? Lembrando que uso uma b450 tomahalk, pretendo pegar no aliexpress, amd deve oferecer reembolso do valor da nota fiscal mais correção, não queria completar muito mais grana além (deve ficar em 1200.00 visto que paguei 850 nele em 2019)

Creio que a melhor opção próximo dos R$1.200 é o Ryzen 5 3600.

É válido pensar no Ryzen 5 5600X que se aproxima do Ryzen 7 3700X em alguns cenários, um pouco mais caro, mas é possível encontrar de vez em quando em promoções por cerca de R$1.800.

Ambas as arquiteturas AMD ZEN4 e RDNA3 devem ser lançadas no quarto trimestre de 2022

AMD Ryzen 7000 e Radeon 7000 serão lançados ao mesmo tempo?

De acordo com o tweet mais recente de @ Broly_X1, que vazou roteiros internos da AMD antes, as arquiteturas de CPU e GPU de próxima geração da AMD estão programadas para serem lançadas ao mesmo tempo.

AMD ZEN4 and RDNA3 architectures both rumored to launch in Q4 2022 - VideoCardz.com

AMD Ryzen 7000 and Radeon 7000 to both launch at the same time? According to the most recent tweet from @Broly_X1, who has leaked AMD internal roadmaps before, the next-gen CPU and GPU architectures from AMD are both slated to launch around the same time. At Computex, AMD has not released a...

Na Computex, a AMD não lançou um novo roteiro, que confirmaria o cronograma de lançamento de suas próximas arquiteturas de CPU e GPU. Oficialmente, a arquitetura Zen4 baseada na tecnologia de processo de 5nm deve ser lançada no final de 2022, pelo menos é o que o roteiro oficial parece sugerir. A AMD também não fez comentários sobre os rumores recentes do Zen4 Raphael. Este codinome está associado a CPUs de desktop baseadas no soquete AM5, agora supostamente chegando no quarto trimestre de 2022. O keynote da Computex não forneceu uma atualização no roteiro de arquitetura de GPU.

Broly_X1 previu / vazou corretamente quase toda a palestra da Computex. Na verdade, ele até mencionou o lançamento do Radeon Pro de amanhã antes de ser oficialmente confirmado. Claramente, suas fontes não podem ser ignoradas. O vazador agora acredita que o quarto trimestre de 2022 é o momento em que devemos ver as CPUs Zen4 e também as GPUs RDNA3. Ele esclareceu ainda que o RDNA3 deve ser gravado ainda este ano.

O vazador também espera uma atualização do Zen3 XT no início de 2021, o que provavelmente preencherá o vazio antes que Raphael chegue no final do próximo ano. Quando se trata de GPUs, porém, não há rumores sobre uma possível atualização, o que pode significar que a série Radeon RX 6000 está aqui para ficar por pelo menos um ano e meio ainda.

Nesse caso acho que o 3700x compensa mais, principalmente por ser mais barato.Creio que a melhor opção próximo dos R$1.200 é o Ryzen 5 3600.

É válido pensar no Ryzen 5 5600X que se aproxima do Ryzen 7 3700X em alguns cenários, um pouco mais caro, mas é possível encontrar de vez em quando em promoções por cerca de R$1.800.

Em produtividade os 2 cores fazem uma bela diferença, no melhor dos casos o 5600x consegue se igualar, mas é raro e no geral o 3700x sai na frente. Único caso que o 5600x compensa é se o foco da pessoa for jogar.

com certeza, pra esse uso entre 3XXX e 5XXX vai ser sair o melhor o que tiver mais cores.Nesse caso acho que o 3700x compensa mais, principalmente por ser mais barato.

Em produtividade os 2 cores fazem uma bela diferença, no melhor dos casos o 5600x consegue se igualar, mas é raro e no geral o 3700x sai na frente. Único caso que o 5600x compensa é se o foco da pessoa for jogar.

Nesse caso acho que o 3700x compensa mais, principalmente por ser mais barato.

Em produtividade os 2 cores fazem uma bela diferença, no melhor dos casos o 5600x consegue se igualar, mas é raro e no geral o 3700x sai na frente. Único caso que o 5600x compensa é se o foco da pessoa for jogar.

3700X foge muito do orçamento dele, por isso recomendei o 5600X como opção mais parruda que o 3600.

5600X hoje na Amazon estava R$1.700, faz tempo que não vejo o 3700X por menos de R$2.000.

Ah, justo então. Tô por fora dos preços e peguei meio 3700x no ali, então foi algo bem mais próximo do orçamento dele (e tava bem mais barato que o 5600x na época).3700X foge muito do orçamento dele, por isso recomendei o 5600X como opção mais parruda que o 3600.

5600X hoje na Amazon estava R$1.700, faz tempo que não vejo o 3700X por menos de R$2.000.

AMD 3D V-Cache é surpreendente

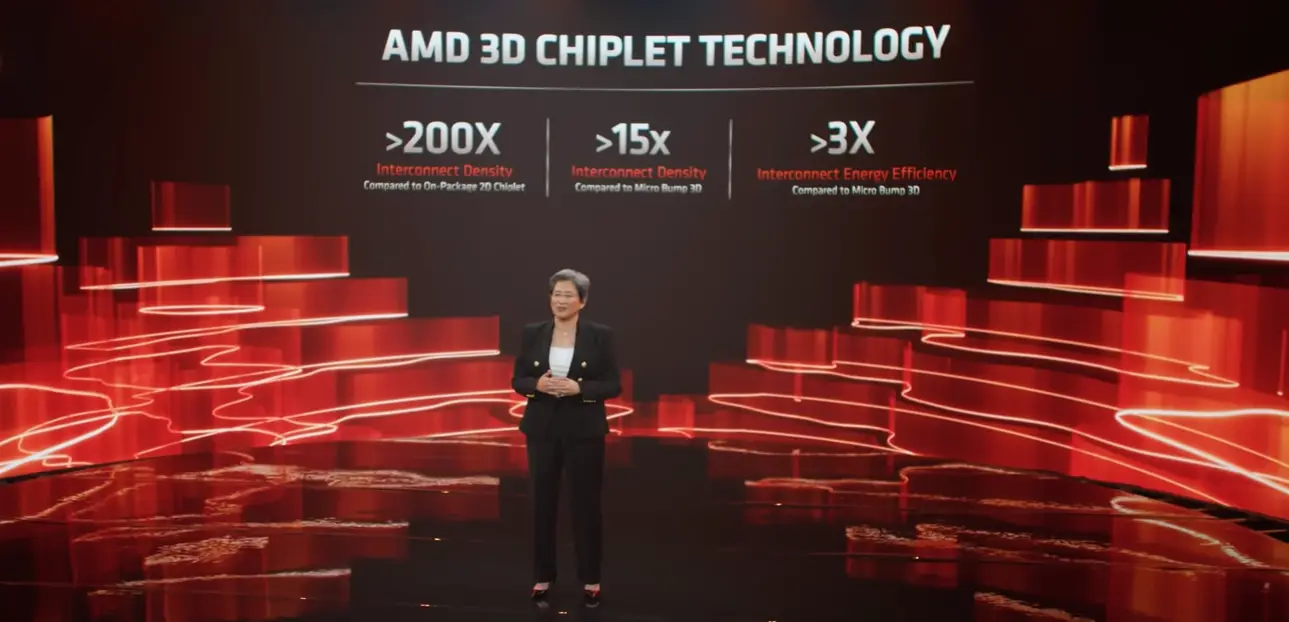

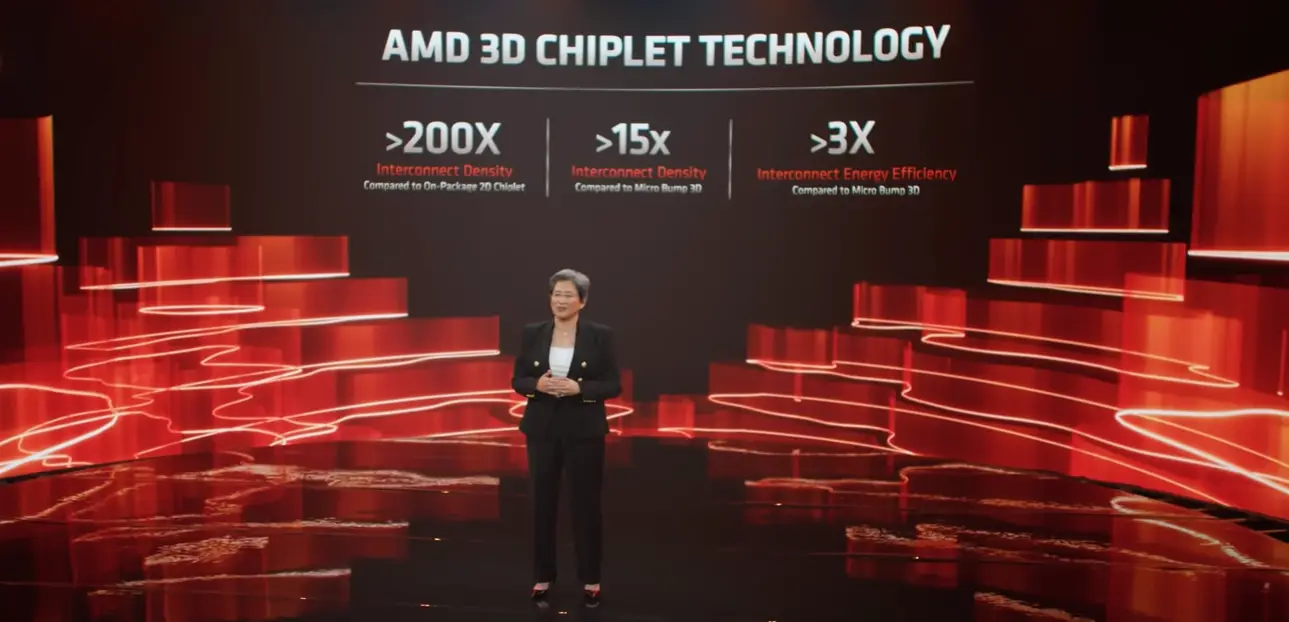

A Dr. Su passou a divulgar algumas tecnologias-chave adicionais envolvidas aqui. “Estamos usando uma abordagem de hybrid bonding com via de silício que fornece mais de 200 vezes a densidade de interconexão de chips 2D e possui mais de 15 vezes de densidade se comparado com outras soluções de empilhamento 3D ."

A geração atual de Foveros da Intel - como como aquele encontrado em Lakefield - usa 50 um pitch micro-bumps que rendem uma densidade de aproximadamente 400 connections / mm².

Tem 15 vezes mais densidade se comparado com a geração atual da Foveros da INTEL, isso implica em torno de > 6.000 connections / mm² .

fuse.wikichip.org

fuse.wikichip.org

Na semana passada, a Computex Taipei 2021 foi realizada virtualmente. Embora o evento tenha sido um sucesso ou um fracasso entre os fornecedores de chips, um dos anúncios mais interessantes que foram entregues no evento foi o 3D V-Cache da AMD - um SRAM 3D empilhado. Mas, embora a SRAM empilhada seja interessante o suficiente, o verdadeiro anúncio foi a introdução da DBI na produção em massa em seus chips de ponta no próximo ano.

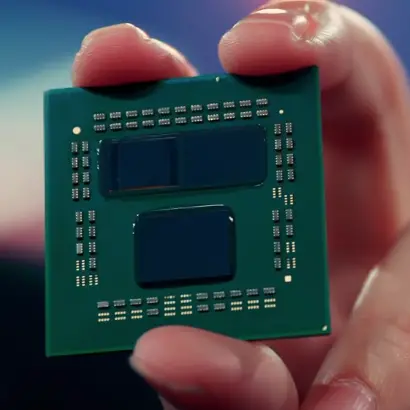

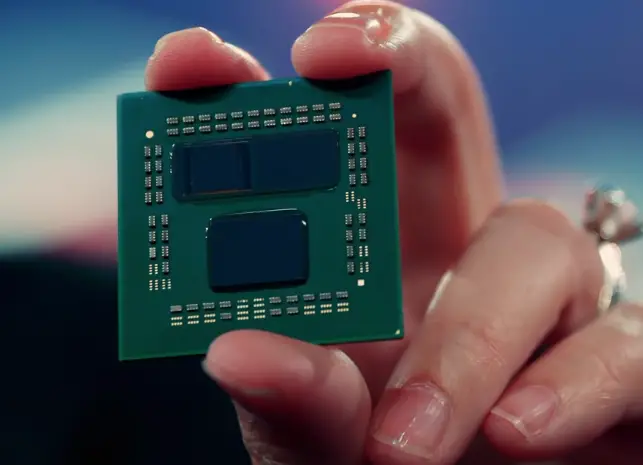

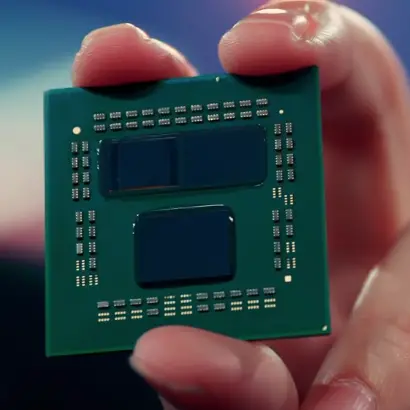

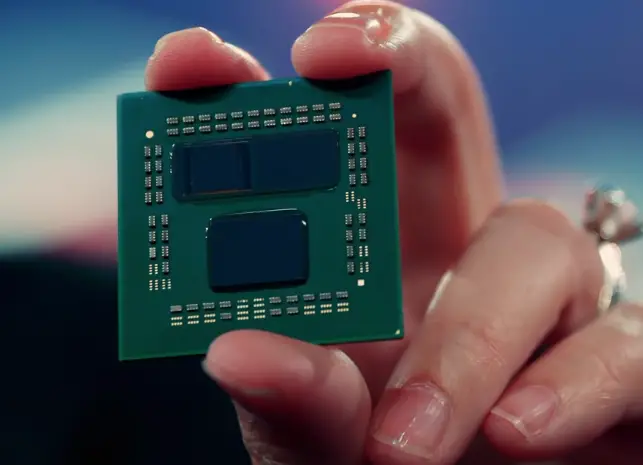

Abaixo está uma foto do Dr. Su segurando um protótipo de chip com o CCD esquerdo exposto, mostrando o die SRAM.

O próprio molde V-Cache 3D de 64 MiB mede 36 mm² (um quadrado de 6 mm x 6 mm). Isso é aproximadamente 9 mm² a mais do que os 32 MiB de L3 no CCD, que ocupa cerca de 27 mm² de silício, então a SRAM no 3D V-Cache parece estar mais compacta. Arquitetonicamente, o próprio dado V-Cache adiciona 64 MiB de capacidade SRAM diretamente sobre os 32 MiB existentes de L3 para um único grande, 96 MiB de capacidade L3. Um chip completo com dois CCDs teria, portanto, uma capacidade L3 máxima de 192 MiB por processador. A largura de banda L3 é considerada triplicada para 2 TB / segundo, mantendo a mesma latência.

Como parte da divulgação do 3D V-Cache, o Dr. Su passou a divulgar algumas tecnologias-chave adicionais envolvidas aqui. “Estamos usando uma abordagem de hybrid bonding com via de silício que fornece mais de 200 vezes a densidade de interconexão de chips 2D e mais de 15 vezes a densidade em comparação com outras soluções de empilhamento 3D. Na verdade, isso permite uma integração muito mais eficiente e densa de nosso IP ”, disse o Dr. Su.

Observe que a densidade de interconexão> 200x se refere ao "chip 2D no pacote" (presumivelmente MCP padrão). O slide mostrado na época dizia especificamente “comparado ao micro bump 3D” quando ela se referia a “outras soluções de empilhamento 3D” para densidade e energia. “A interface die-to-die usa uma ligação direta cobre-cobre sem bump de solda de qualquer tipo. Essa abordagem melhora drasticamente as térmicas, a densidade do transistor e o pitch de interconexão e é apenas um terço da energia por sinal das abordagens 3D de micro-bumps ”, acrescentou ela. “Todas essas coisas tornam esta realmente a tecnologia de empilhamento ativo-sobre-ativo mais avançada e flexível do mundo.”

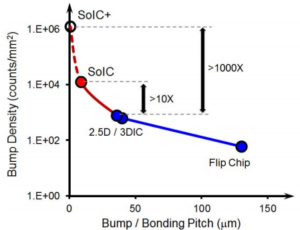

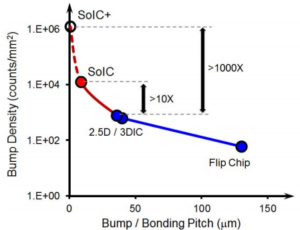

Em um MCP típico como o que a AMD usa, estamos observando cerca de 100 bumps / mm². Em comparação, a geração atual de Foveros da Intel - como a encontrada em Lakefield - usa micro-saliências de 50 um, que geram uma densidade de aproximadamente 400 connections / mm². 15 vezes a densidade em comparação com a geração atual de Foveros implica em torno de> 6.000 connections / mm². A TSMC relatou um pitch de títulos superior a 10.000 para seu SoIC, então isso parece mais ou menos onde você esperaria que o DBI de primeira geração estivesse. A hybrid bonding menor que 10 mícrons pode exceder em muito 10.000 conexões (por exemplo, a Sony já excede o passo de 4 mícrons em 2019 em seus sensores de imagem). A Intel anunciou sua potência para Lakefield em torno de 0,15 pJ / bit. As conexões V-Cache estariam em torno de 0,05 pJ / bit ou cerca de um terço. É importante ressaltar que o Foveros da Intels tem uma série de gerações futuras, incluindo micro-bumps até 25 mícrons (e densidade superior a 1600 conexões / mm²), bem como várias implementações de ligação direta de 10 mícrons e abaixo de semelhantes aos de TSMC, embora nenhum produto ainda foi anunciado para utilizar essas tecnologias. Outras empresas, como a GlobalFoundries, também anunciaram tecnologias de hybrid bonding.

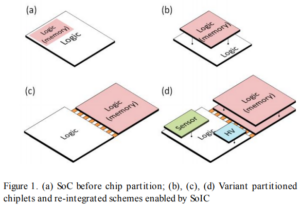

As informações divulgadas implicam que a AMD utilizará a tecnologia System on Integrated Chips (SoIC) da TSMC. SoIC é um termo de marca guarda-chuva usado pela TSMC para descrever um conjunto completo de tecnologias de empilhamento 3D de back-end que, por sua vez, podem ser holisticamente integradas a qualquer outra tecnologia de front-end, como flip-chip (como no caso da AMD ), CoWoS ou InFO. Uma característica especial do SoIC é seu passo de ligação altamente denso, atingindo sub-10 μm.

A Dr. Su passou a divulgar algumas tecnologias-chave adicionais envolvidas aqui. “Estamos usando uma abordagem de hybrid bonding com via de silício que fornece mais de 200 vezes a densidade de interconexão de chips 2D e possui mais de 15 vezes de densidade se comparado com outras soluções de empilhamento 3D ."

A geração atual de Foveros da Intel - como como aquele encontrado em Lakefield - usa 50 um pitch micro-bumps que rendem uma densidade de aproximadamente 400 connections / mm².

Tem 15 vezes mais densidade se comparado com a geração atual da Foveros da INTEL, isso implica em torno de > 6.000 connections / mm² .

AMD 3D Stacks SRAM Bumplessly

AMD 3D Stacks SRAM Bumplessly

AMD recently unveiled 3D V-Cache, their first 3D-stacked technology-based product. Leapfrogging contemporary 3D bonding technologies, AMD jumped directly into advanced packaging with direct bonding and an order of magnitude higher wire density.

fuse.wikichip.org

fuse.wikichip.org

Na semana passada, a Computex Taipei 2021 foi realizada virtualmente. Embora o evento tenha sido um sucesso ou um fracasso entre os fornecedores de chips, um dos anúncios mais interessantes que foram entregues no evento foi o 3D V-Cache da AMD - um SRAM 3D empilhado. Mas, embora a SRAM empilhada seja interessante o suficiente, o verdadeiro anúncio foi a introdução da DBI na produção em massa em seus chips de ponta no próximo ano.

3D V-Cache

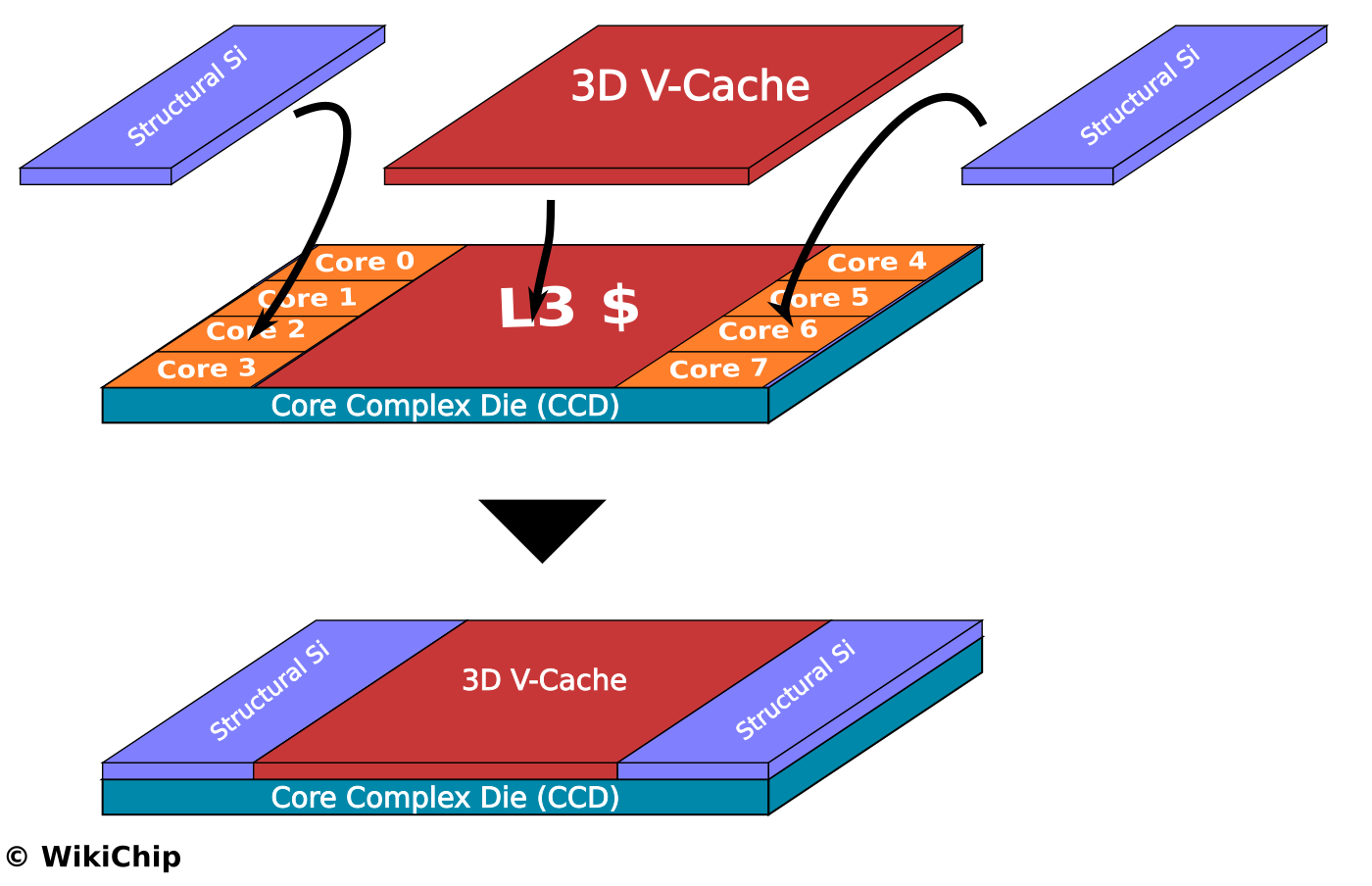

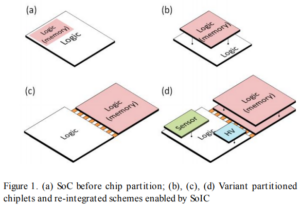

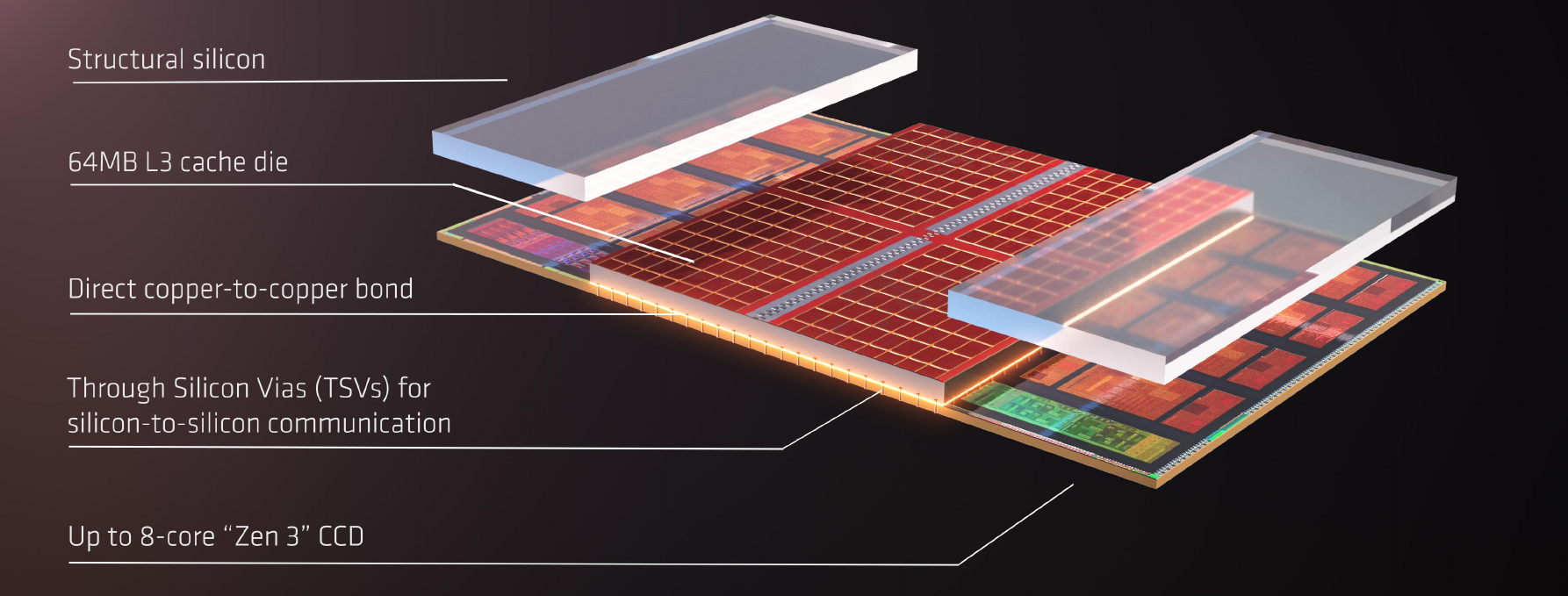

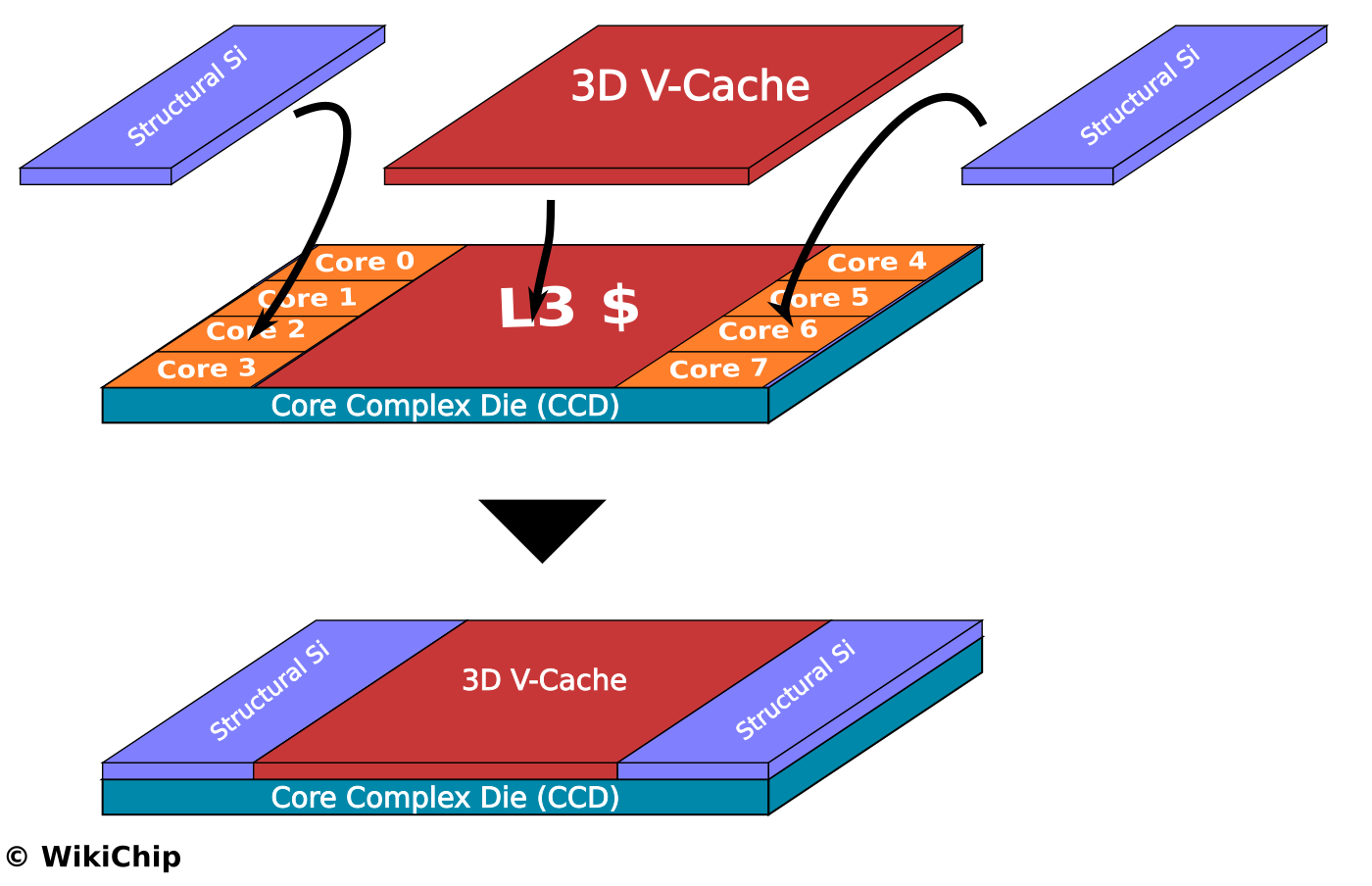

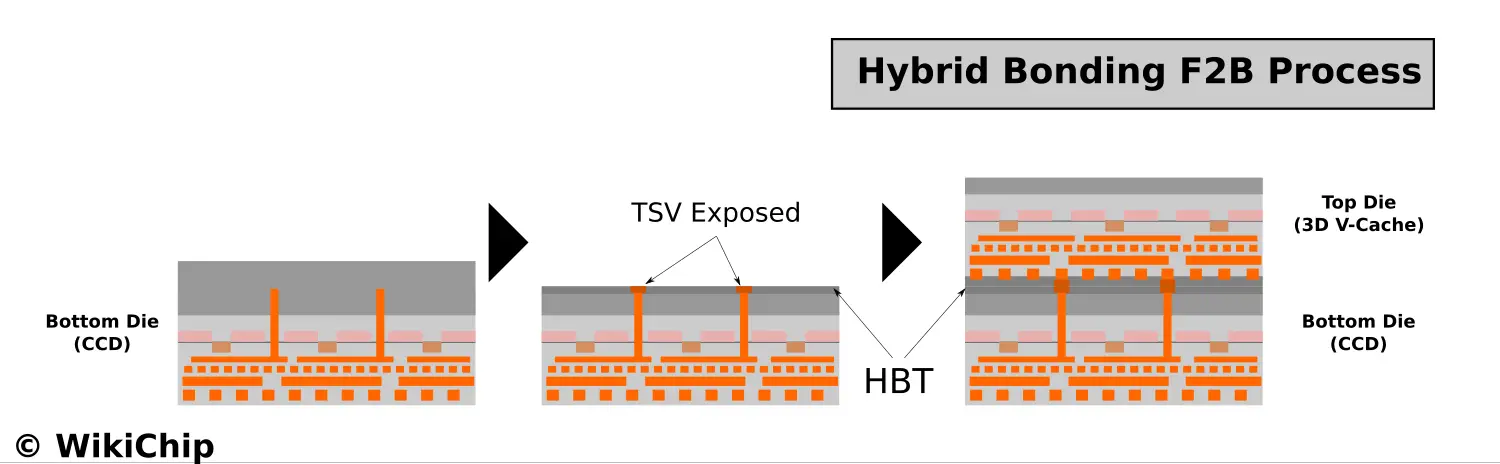

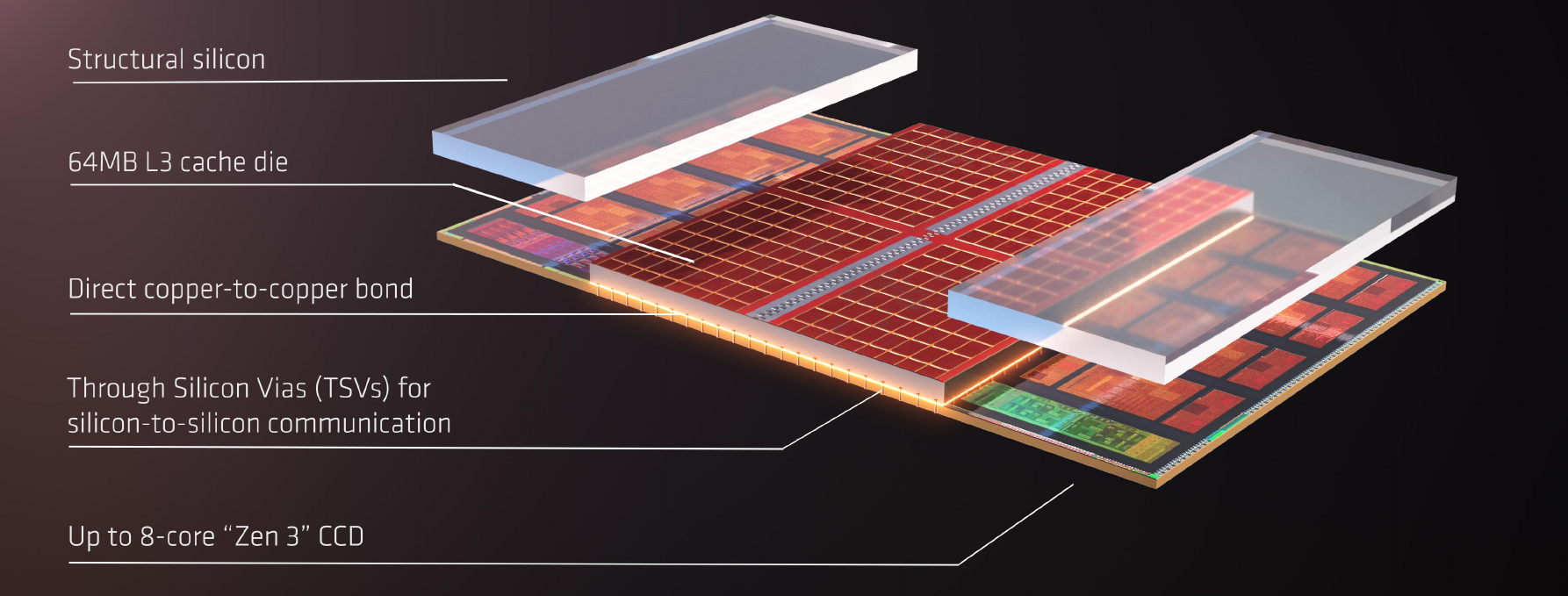

Na parte final do evento da AMD, a presidente e CEO da AMD, Dra. Lisa Su, começou a falar sobre algumas das tecnologias avançadas nas quais a empresa está trabalhando. A AMD divulgou sua primeira aplicação de empilhamento de chips 3D verdadeiro, que eles chamaram de “3D V-Cache”.Um protótipo de chip também foi mostrado no evento. A AMD mostrou um microprocessador da série Ryzen 5000 que incorporou o V-Cache. Os microprocessadores da série Ryzen 5000 incorporam um ou dois Core Complex Dies (CCDs) junto com um Die I / O (IOD). O V-Cache é um dado SRAM de 64 MiB fabricado no processo de 7 nanômetros da TSMC. O dado V-Cache é diluído e então empilhado diretamente no topo de cada CCD diretamente acima da área de cache L3 existente. Nos microprocessadores da série Ryzen 5000, cada CCD possui 32 MiB de cache L3, portanto, o V-Cache efetivamente triplica a capacidade L3 de cada CPU. Duas dies estruturais adicionais são adicionadas no topo dos CCDs acima do complexo da CPU. Não se sabe se essas dies estruturais são de silício em branco ou se incluem algo especial (por exemplo,

Abaixo está uma foto do Dr. Su segurando um protótipo de chip com o CCD esquerdo exposto, mostrando o die SRAM.

O próprio molde V-Cache 3D de 64 MiB mede 36 mm² (um quadrado de 6 mm x 6 mm). Isso é aproximadamente 9 mm² a mais do que os 32 MiB de L3 no CCD, que ocupa cerca de 27 mm² de silício, então a SRAM no 3D V-Cache parece estar mais compacta. Arquitetonicamente, o próprio dado V-Cache adiciona 64 MiB de capacidade SRAM diretamente sobre os 32 MiB existentes de L3 para um único grande, 96 MiB de capacidade L3. Um chip completo com dois CCDs teria, portanto, uma capacidade L3 máxima de 192 MiB por processador. A largura de banda L3 é considerada triplicada para 2 TB / segundo, mantendo a mesma latência.

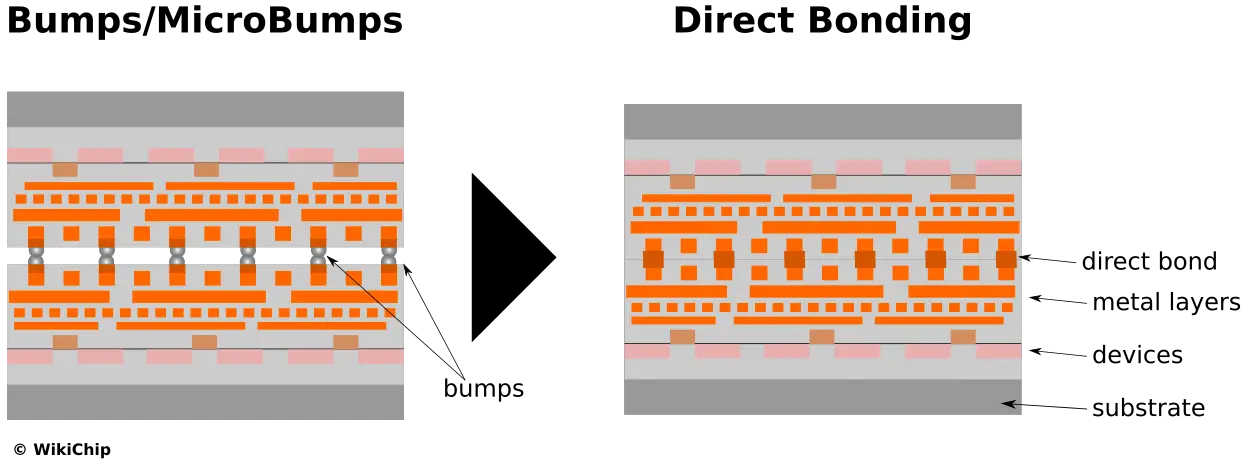

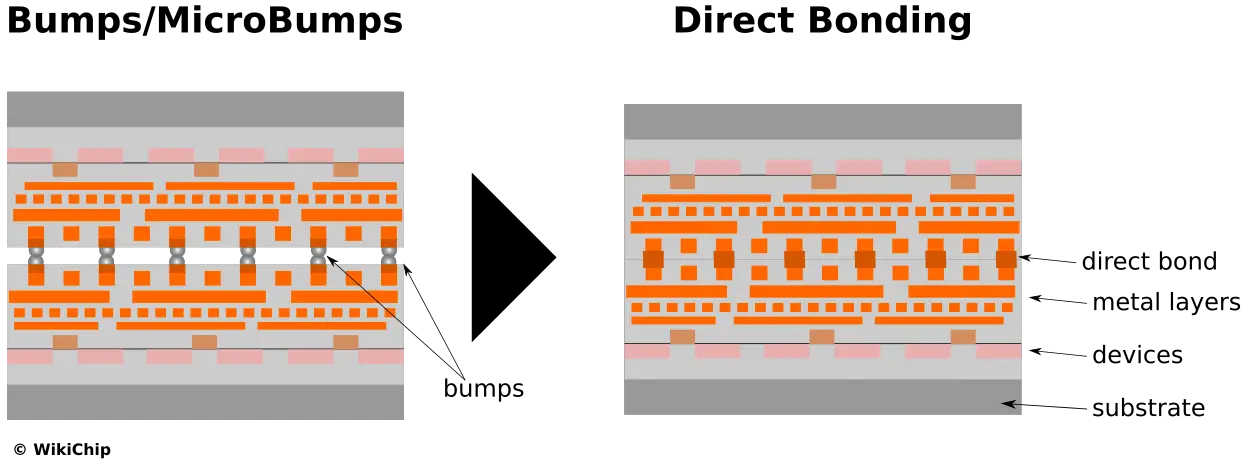

Comercialização DBI em lógica de alto desempenho

Embora a SRAM empilhada seja interessante, a grande novidade parece ser a mudança para a interconexão de títulos diretos, ou DBI. DBI ou hybrid bonding é uma ligação permanente das interconexões de cobre incorporadas diretamente, sem bumps ou pillars. Esta não é a primeira vez que DBI é usado (a Sony, por exemplo, o usou pela primeira vez no IMX260 que foi usado no Samsung Galaxy S7 em 2016), mas esta parece ser a primeira vez que é usado em alta aplicativos de lógica de desempenho.

Como parte da divulgação do 3D V-Cache, o Dr. Su passou a divulgar algumas tecnologias-chave adicionais envolvidas aqui. “Estamos usando uma abordagem de hybrid bonding com via de silício que fornece mais de 200 vezes a densidade de interconexão de chips 2D e mais de 15 vezes a densidade em comparação com outras soluções de empilhamento 3D. Na verdade, isso permite uma integração muito mais eficiente e densa de nosso IP ”, disse o Dr. Su.

Observe que a densidade de interconexão> 200x se refere ao "chip 2D no pacote" (presumivelmente MCP padrão). O slide mostrado na época dizia especificamente “comparado ao micro bump 3D” quando ela se referia a “outras soluções de empilhamento 3D” para densidade e energia. “A interface die-to-die usa uma ligação direta cobre-cobre sem bump de solda de qualquer tipo. Essa abordagem melhora drasticamente as térmicas, a densidade do transistor e o pitch de interconexão e é apenas um terço da energia por sinal das abordagens 3D de micro-bumps ”, acrescentou ela. “Todas essas coisas tornam esta realmente a tecnologia de empilhamento ativo-sobre-ativo mais avançada e flexível do mundo.”

Em um MCP típico como o que a AMD usa, estamos observando cerca de 100 bumps / mm². Em comparação, a geração atual de Foveros da Intel - como a encontrada em Lakefield - usa micro-saliências de 50 um, que geram uma densidade de aproximadamente 400 connections / mm². 15 vezes a densidade em comparação com a geração atual de Foveros implica em torno de> 6.000 connections / mm². A TSMC relatou um pitch de títulos superior a 10.000 para seu SoIC, então isso parece mais ou menos onde você esperaria que o DBI de primeira geração estivesse. A hybrid bonding menor que 10 mícrons pode exceder em muito 10.000 conexões (por exemplo, a Sony já excede o passo de 4 mícrons em 2019 em seus sensores de imagem). A Intel anunciou sua potência para Lakefield em torno de 0,15 pJ / bit. As conexões V-Cache estariam em torno de 0,05 pJ / bit ou cerca de um terço. É importante ressaltar que o Foveros da Intels tem uma série de gerações futuras, incluindo micro-bumps até 25 mícrons (e densidade superior a 1600 conexões / mm²), bem como várias implementações de ligação direta de 10 mícrons e abaixo de semelhantes aos de TSMC, embora nenhum produto ainda foi anunciado para utilizar essas tecnologias. Outras empresas, como a GlobalFoundries, também anunciaram tecnologias de hybrid bonding.

SoIC

As informações divulgadas implicam que a AMD utilizará a tecnologia System on Integrated Chips (SoIC) da TSMC. SoIC é um termo de marca guarda-chuva usado pela TSMC para descrever um conjunto completo de tecnologias de empilhamento 3D de back-end que, por sua vez, podem ser holisticamente integradas a qualquer outra tecnologia de front-end, como flip-chip (como no caso da AMD ), CoWoS ou InFO. Uma característica especial do SoIC é seu passo de ligação altamente denso, atingindo sub-10 μm.

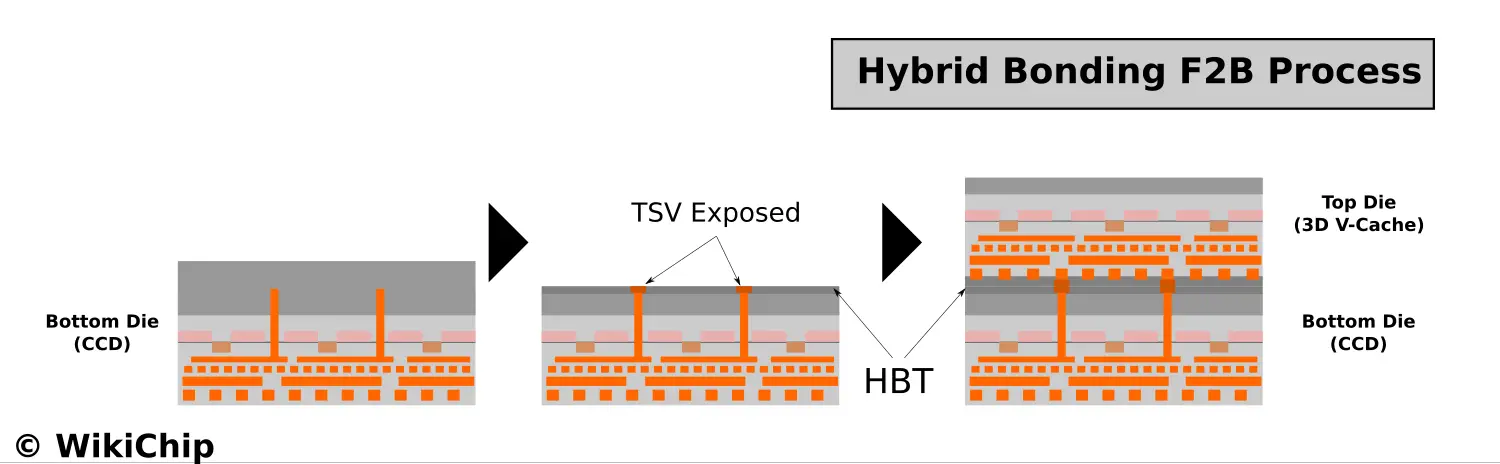

No empilhamento 3D, os chips são interconectados cara a cara ou cara a cara (ou ambos). Se presumirmos que o pacote da série Ryzen 5000 usado não foi alterado, isso significa que eles estão usando um fluxo de ligação frente a frente (com os CCDs voltados para baixo, como de costume). O Dr. Su observou que eles estão usando a hybrid bonding com TSVs, o que implica que este é, de fato, um processo F2B. Sob esse fluxo de processo, você teria o wafer CCD montado em um portador que é afinado para expor os TSVs na parte traseira. O terminal de hybrid bonding é então formado na parte de trás. O die 3D V-Cache também é afinada e, em seguida, fixada com a face para baixo.

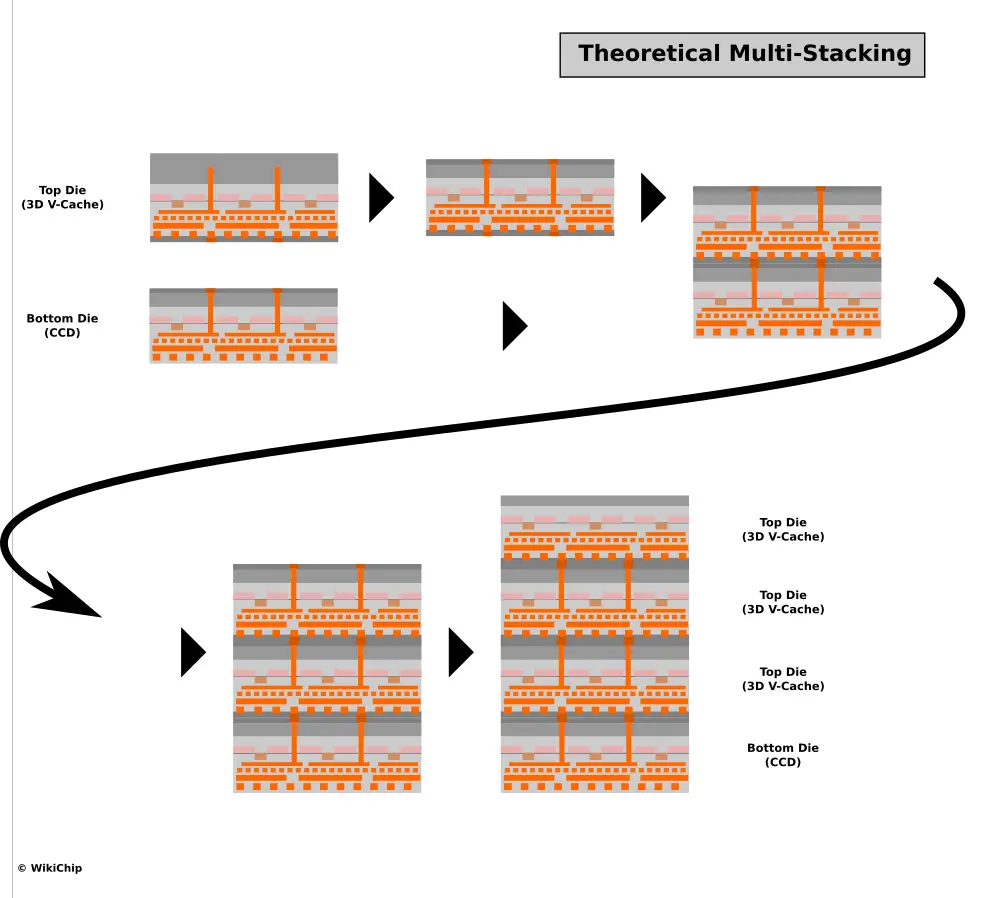

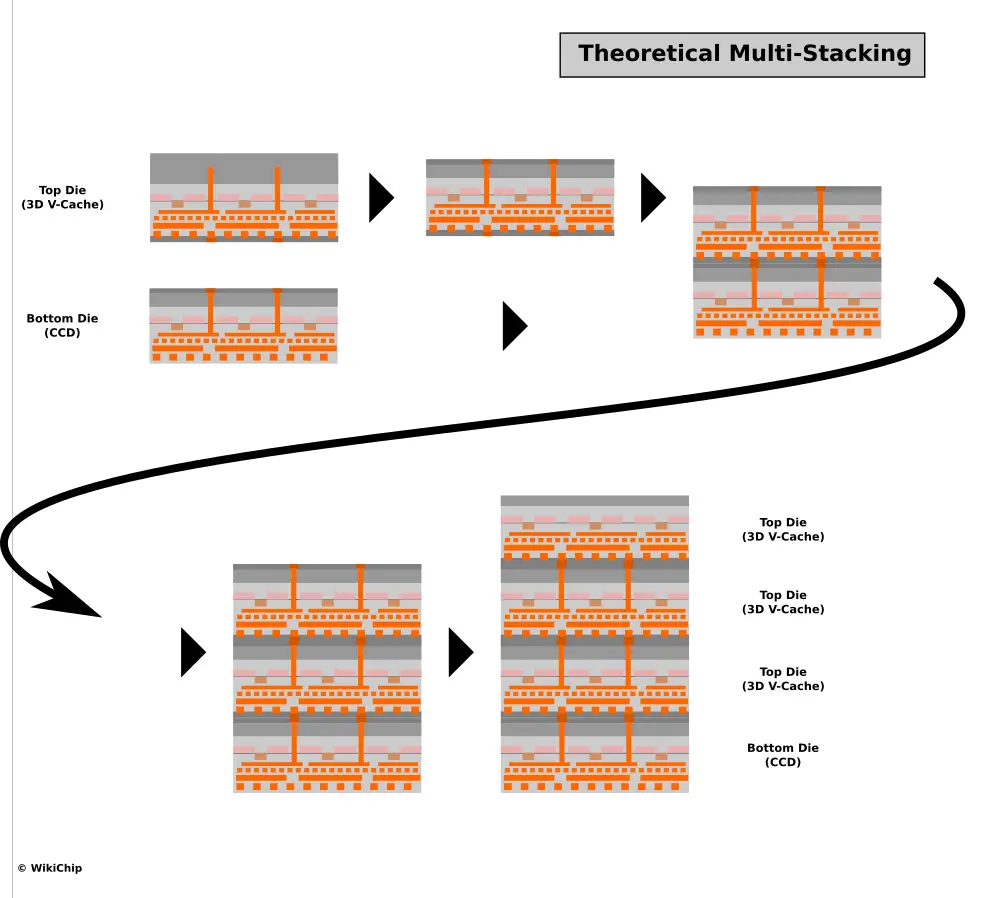

Uma consequência interessante de usar um fluxo F2B - em oposição a um fluxo face a face - é o fato de que esse fluxo de processo é realmente repetível. Em outras palavras, o próprio V-Cache 3D também pode ser reduzido para expor seus próprios TSVs na parte de trás, permitindo que outro dado V-Cache 3D seja conectado com a face para baixo em cima dele. Isso é um pouco semelhante ao HBM empilhado em espírito, mas a tecnologia de embalagem é obviamente muito diferente. Também exigiria a implementação lógica subjacente para suportar tal design. Observe que, atualmente, a AMD está falando apenas sobre um único V-Cache 3D empilhado. No entanto, a possibilidade existe.

Produção por EOY

A AMD disse que espera iniciar a produção até o final do ano. A AMD não revelou quais produtos utilizarão a nova tecnologia, a não ser para dizer que são seus produtos de última geração. A produção iniciada no final deste ano implica que podemos esperar ver a tecnologia nos produtos no início de 2022.

3700X foge muito do orçamento dele, por isso recomendei o 5600X como opção mais parruda que o 3600.

5600X hoje na Amazon estava R$1.700, faz tempo que não vejo o 3700X por menos de R$2.000.

Fala grande mestre !!, faz um guia para gente de PBO e CO para Ryzen 3000 <3

o curve optimizer só funciona nos ryzen 5000Fala grande mestre !!, faz um guia para gente de PBO e CO para Ryzen 3000 <3

o curve optimizer só funciona nos ryzen 5000

nos 3000, não funciona? porque a opção tem..

minha asus b450m pro gamming chegou e o usb 3.0 frontal do gabinete da a mensagem '' dispositivo usb 3.0 nao reconhecido '' quando conecto pen driver, o usb 2.0 funciona normal, o cabo azul esta certinho na placa mae, alguem ja teve esse problema?

Na outra placa mãe a porta frontal do gabinete funcionava normalmente?

A nova placa mãe reconhece o pen-drive 3.0 na BIOS, por exemplo para instalar o Windows?

Está usando uma instalação limpa/nova do Windows?

Drivers de chipset e controladores USB estão atualizados? (AMD e outros, tipo ASMedia... Realtek...).

Tente mudar os ajustes de USB na BIOS.

Atualize a BIOS.

Users who are viewing this thread

Total: 4 (membros: 0, visitantes: 4)