Acho que não mais. Se aparecer novamente aviso.Nossa, essa Asrock tá bem barata mesmo, ainda tem esse preço no Brasa?

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

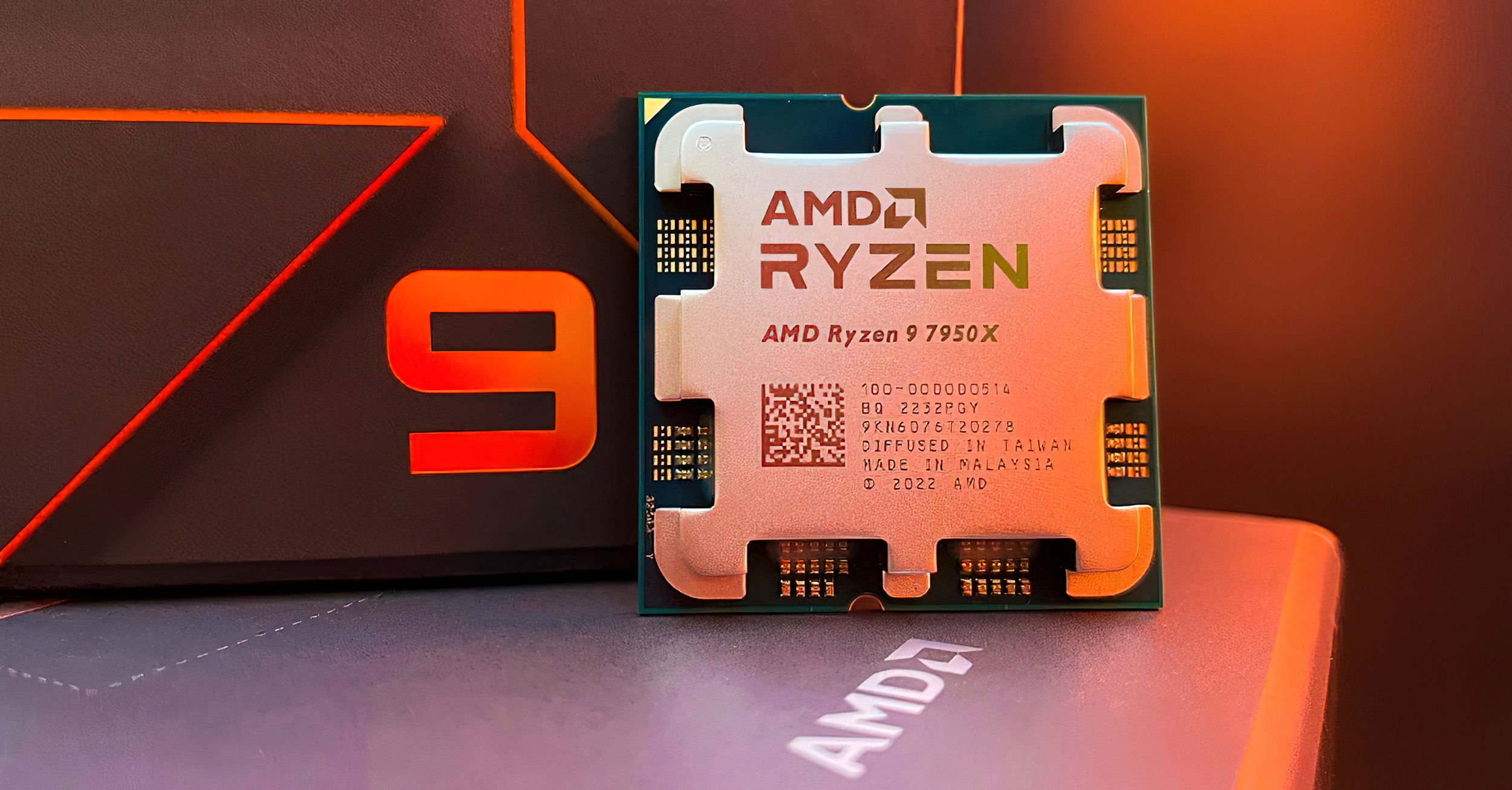

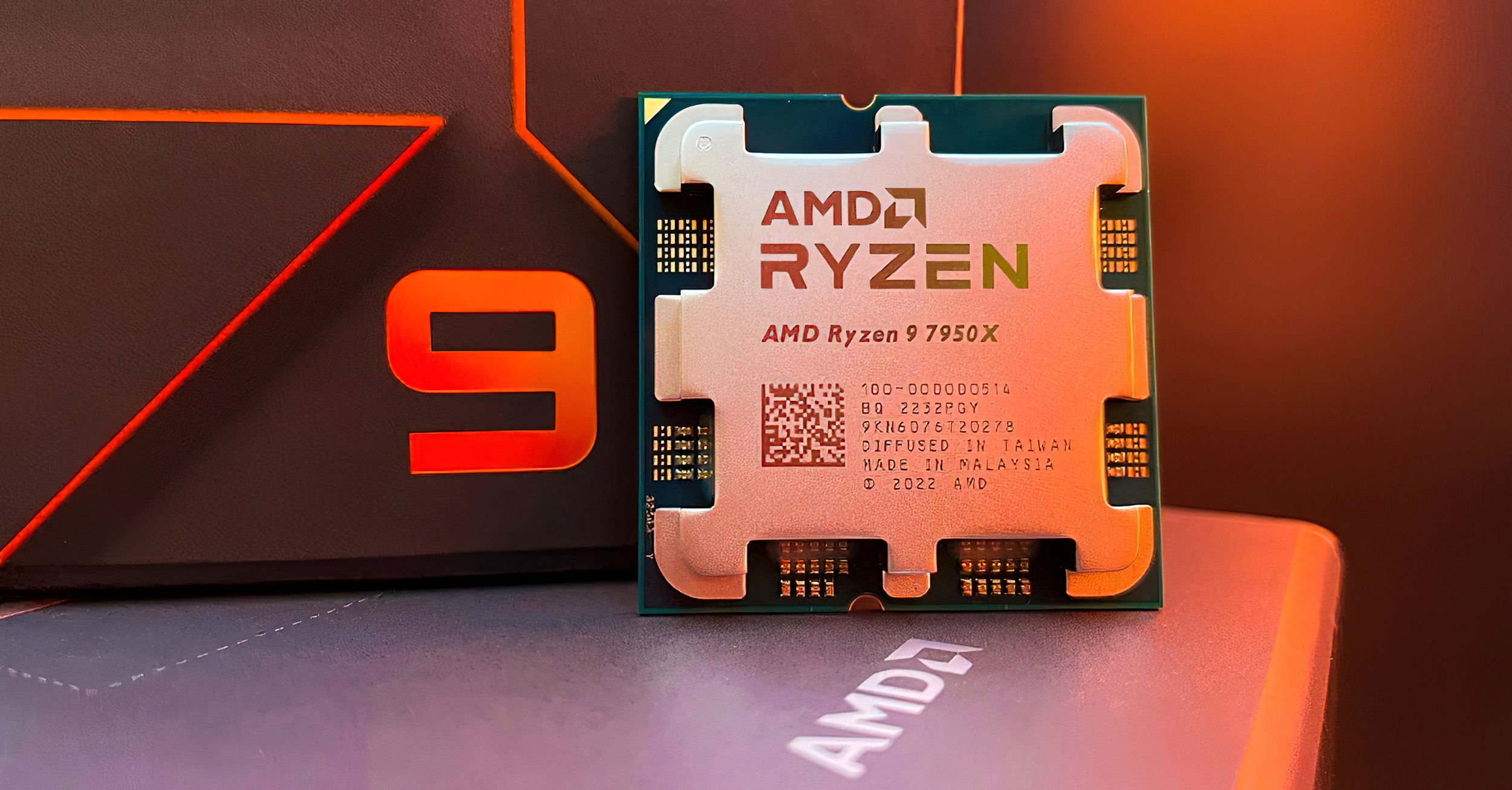

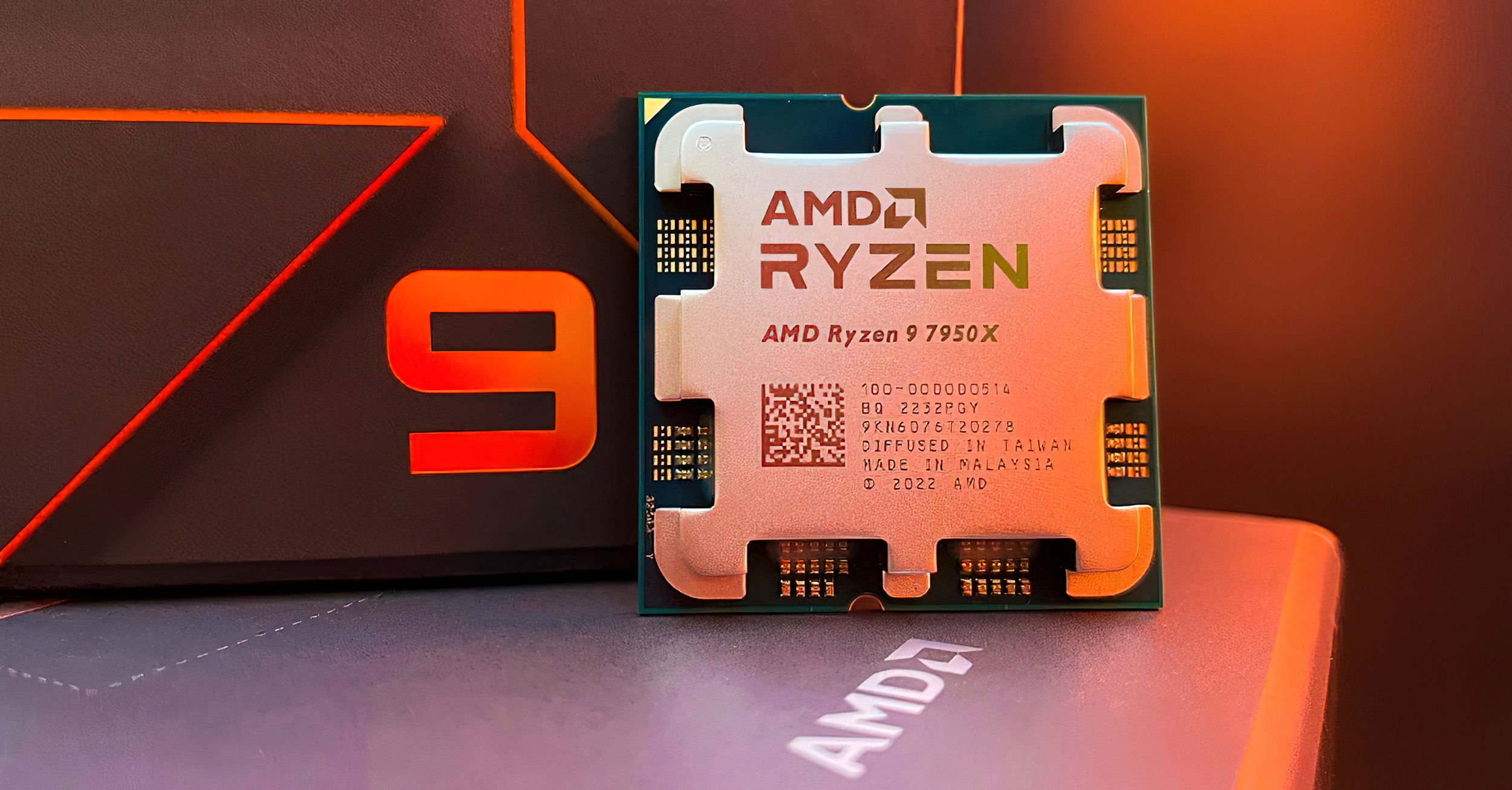

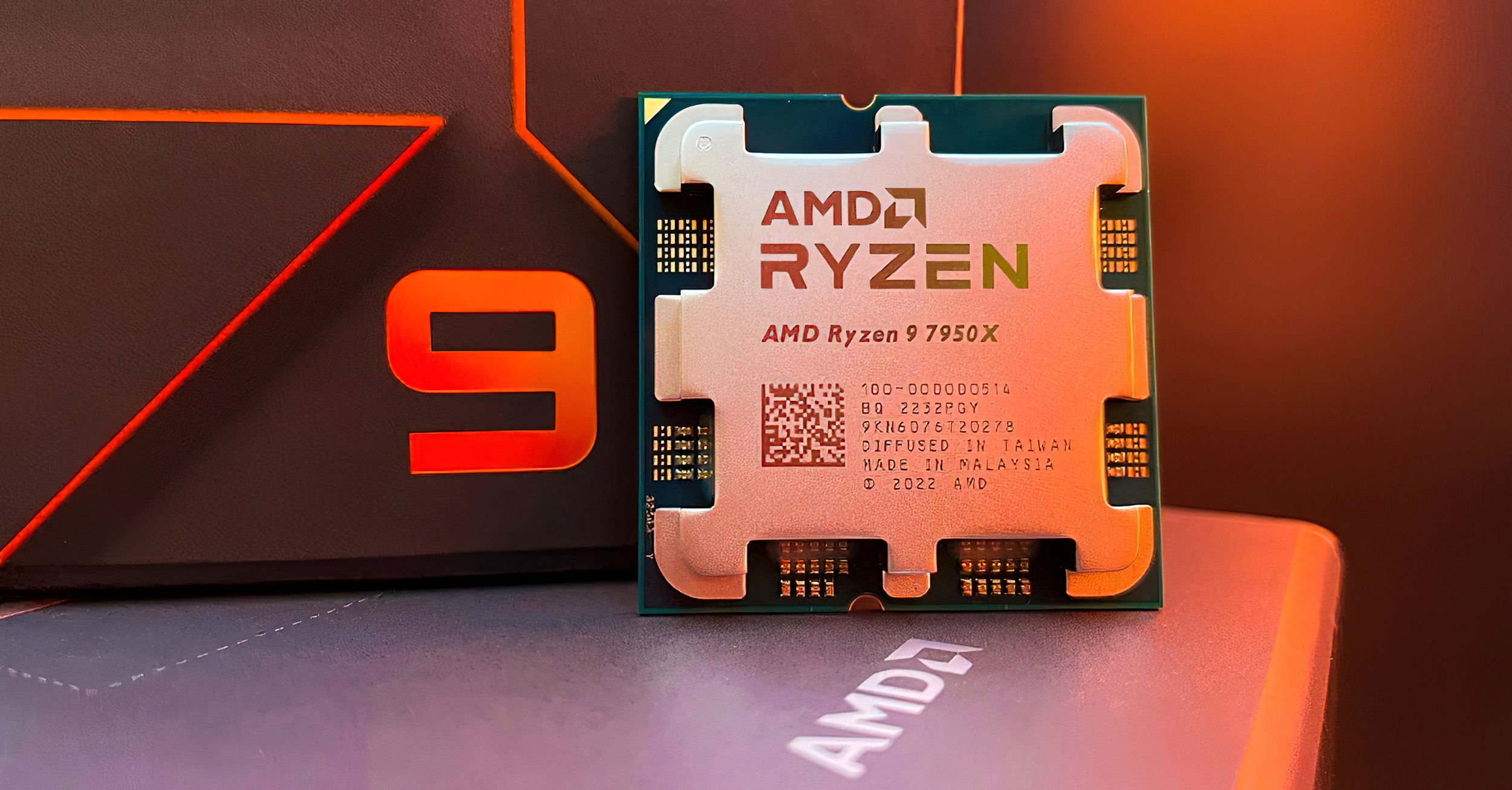

[TÓPICO DEDICADO] AMD Ryzen Socket AM5 - Zen 4, Zen 5 e além

- Iniciador de Tópicos Morello

- Data de Início

Sabia que iriam reduzir, mas não tão rápido..rsrs

O 13900 tirou o reinado absoluto do 7950x, e ainda custava menos.

Agora com essa redução fica interessante novamente

Só falta as placas-mãe e memórias DDR5 caírem mais

E caiu nos EUA também, NewEgg colocou uns descontos bons, seria BlackFriday ou permanente?Capaz de eu viajar e ter price cut.

Brasileiro nao tem um minuto de paz.

AMD Ryzen 7000 gets a major price cut on Newegg, Ryzen 9 7950X now at $574 - VideoCardz.com

AMD Ryzen 7000 deals reach US Newegg leads the Black Friday Week in US sales by introducing new prices for Ryzen 7000 desktop CPUs. Thus far other large US retailers (such as BestBuy or Amazon) have not followed Newegg by lowering the price for Ryzen AM5 CPUs. However, MicroCenter still offers...

Finalmente o 7700X ficou mais barato que o 5800X3D xD

R9 7950X = $699 -> $574

R9 7900X = $549 -> $474

R7 7700X = $399 -> $349

R5 7600X = $299 -> $249

Essa que a Microcenter está dando tem Expo, porém eu vi no Reddit gente que nao deu boot com ela na TUF, ai teve que atualizar a Bios e depois funcionou. Deve ser por ser modelo novo da memória.sobre DDR5 nos Ryzen é importante que o pessoal prefira modelos de memória que suportem EXPO e não apenas XMP, ou então, se você já verificou que no XMP o resultado testado foi normal, tudo bem. Mas tem casos em que o XMP pode não funcionar muito bem e depender de atualização, que sabe-se lá quando virá. E tem o fato de que se muita gente preferir sempre o XMP em detrimento do EXPO, a disponibilidade de memórias testadas para AMD pode ter queda considerável, sendo que o EXPO é uma necessidade para resolver boa parcela de problemas com memórias evitando o que acontecia nas DDR4: falta de teste na plataforma AMD.

no yt tem uma ou outra pessoa que diz ter testado nos ryzens clocks de 7200MHz com duas memórias e 5200MHz com quatro, mas sem maiores detalhes.

Um comprador da Amazon.US reportou que adquiriu um Ryzen 9 7950x e colocou 128GB DDR5 numa ASRock X670E Steel Legend e teve problemas de boot muito demorado. Bom, ao menos o primeiro grande problema dele é esse:

G.Skill Trident Z5 Series (Intel XMP) 64GB (2 x 32GB) 288-Pin SDRAM DDR5 6000 CL32-38-38-96 1.40V Dual Channel Desktop Memory F5-6000J3238G32GX2-TZ5S (Metallic Silver)

Essa memória é SOMENTE XMP, então testada para a plataforma Intel. Embora ele diga que depois o sistema fica estável.

E sim, o boot inicial vai demorar quanto mais memória tiver, ainda que a memória seja compatível com EXPO, porém é de se esperar que as próximas inicializações sejam mais rápidas.

Ta dando pra chegar em 7200? Vi o pessoal falando em 6400 nas Hynix.

Se esses preços forem permanentes é de se esperar que os futuros 7600 e 7700 não X devem vir por 199 e 200 dólares, respectivamente.E caiu nos EUA também, NewEgg colocou uns descontos bons, seria BlackFriday ou permanente?

AMD Ryzen 7000 gets a major price cut on Newegg, Ryzen 9 7950X now at $574 - VideoCardz.com

AMD Ryzen 7000 deals reach US Newegg leads the Black Friday Week in US sales by introducing new prices for Ryzen 7000 desktop CPUs. Thus far other large US retailers (such as BestBuy or Amazon) have not followed Newegg by lowering the price for Ryzen AM5 CPUs. However, MicroCenter still offers...videocardz.com

Finalmente o 7700X ficou mais barato que o 5800X3D xD

R9 7950X = $699 -> $574

R9 7900X = $549 -> $474

R7 7700X = $399 -> $349

R5 7600X = $299 -> $249

A NewEgg tinha anunciado esse preço do 7950x como desconto da BF.E caiu nos EUA também, NewEgg colocou uns descontos bons, seria BlackFriday ou permanente?

AMD Ryzen 7000 gets a major price cut on Newegg, Ryzen 9 7950X now at $574 - VideoCardz.com

AMD Ryzen 7000 deals reach US Newegg leads the Black Friday Week in US sales by introducing new prices for Ryzen 7000 desktop CPUs. Thus far other large US retailers (such as BestBuy or Amazon) have not followed Newegg by lowering the price for Ryzen AM5 CPUs. However, MicroCenter still offers...videocardz.com

Finalmente o 7700X ficou mais barato que o 5800X3D xD

R9 7950X = $699 -> $574

R9 7900X = $549 -> $474

R7 7700X = $399 -> $349

R5 7600X = $299 -> $249

Última edição:

Tomara que não seja só para a BFE caiu nos EUA também, NewEgg colocou uns descontos bons, seria BlackFriday ou permanente?

AMD Ryzen 7000 gets a major price cut on Newegg, Ryzen 9 7950X now at $574 - VideoCardz.com

AMD Ryzen 7000 deals reach US Newegg leads the Black Friday Week in US sales by introducing new prices for Ryzen 7000 desktop CPUs. Thus far other large US retailers (such as BestBuy or Amazon) have not followed Newegg by lowering the price for Ryzen AM5 CPUs. However, MicroCenter still offers...videocardz.com

Finalmente o 7700X ficou mais barato que o 5800X3D xD

R9 7950X = $699 -> $574

R9 7900X = $549 -> $474

R7 7700X = $399 -> $349

R5 7600X = $299 -> $249

para as primeiras BIOS havia alguns problemas, mas resolveram e, ao que vejo, tem funcionado bem em XMP também, entretanto, com maiores riscos, então, EXPO é mais garantido mesmo porque FOIT TESTADO de fato na plataforma AMD, enquanto XMP NÃO É, pois é um padrão para a controladora da Intel.Essa que a Microcenter está dando tem Expo, porém eu vi no Reddit gente que nao deu boot com ela na TUF, ai teve que atualizar a Bios e depois funcionou. Deve ser por ser modelo novo da memória.

Ta dando pra chegar em 7200? Vi o pessoal falando em 6400 nas Hynix.

Esse clock de 7200MHz é de um canal que faz testes em games, não vi detalhes específicos, mas um cara na Amazon.us estava rodando, com problema de boot lento, 128GB em 6000MHz e o porém é que ele acusou a placa-mãe da Asrock ao invés de se tocar que o problema mesmo é que ele pegou a versão XMP exclusivo para Intel. Ele mesmo poderia resolver o problema ajustando manualmente os timings, mas isso é uma trabalheira infinita que não vale a pena.

portanto, ATENÇÃO em comprar MEMÓRIA DDR5 EXPO para processadores AMD!

--- Post duplo é unido automaticamente: ---

melhor é o R9 7950x, se vier a memória grátis tb.Melhor é R7 7700x com memoria grátis ou R9 7900x com memoria grátis.

Esse R9 7950x é um monstro.

Também na Amazon US e UK:E caiu nos EUA também, NewEgg colocou uns descontos bons, seria BlackFriday ou permanente?

AMD Ryzen 7000 gets a major price cut on Newegg, Ryzen 9 7950X now at $574 - VideoCardz.com

AMD Ryzen 7000 deals reach US Newegg leads the Black Friday Week in US sales by introducing new prices for Ryzen 7000 desktop CPUs. Thus far other large US retailers (such as BestBuy or Amazon) have not followed Newegg by lowering the price for Ryzen AM5 CPUs. However, MicroCenter still offers...videocardz.com

Finalmente o 7700X ficou mais barato que o 5800X3D xD

R9 7950X = $699 -> $574

R9 7900X = $549 -> $474

R7 7700X = $399 -> $349

R5 7600X = $299 -> $249

Galera que ta mais por dentro do assunto.

Preciso de uma ajudinha de vocês!

Trabalho muito com renders 3D, AutoCAD, Corel, Illustrator e também sou partner da Twitch (streamer) e ando fazendo 80% home-office no meu dia-a-dia tenho uma maquina boa (8700K+3070+16gb ram) a parte de que eu tenho que subir a ram para 32GB ja não me é novidade, só que mesmo dizendo isso, a maquina ta começando a apresentar os sinais da idade até por conta que nem todo o conteudo do meu canal pode ser transmitido por Full Nvenc, quando eu uso o PS5 o Nvenc fica exclusivo para encodar a placa de captura para o OBS, consequencia que o nVENC fica travado e sou obrigado a usar o x264 (CPU) e também devo mirar o AV1 que está a caminho, então o ideal é que eventualmente eu terei de ter AV1 na GPU e na CPU.

O ponto crucial dessa curva, é que como to usando muito da minha maquina, estou colocando na balança de fazer um investimento pesado, para ganhar mais tempo no meu dia-a-dia.

No meu caso, partir logo pra um 7950X ou qualquer coisa agressiva desse ponto seria worth update?

:::Acho que postei em area errada:::, fiz a mesma pergunta numa area mais apropriada, my bad!:::

Preciso de uma ajudinha de vocês!

Trabalho muito com renders 3D, AutoCAD, Corel, Illustrator e também sou partner da Twitch (streamer) e ando fazendo 80% home-office no meu dia-a-dia tenho uma maquina boa (8700K+3070+16gb ram) a parte de que eu tenho que subir a ram para 32GB ja não me é novidade, só que mesmo dizendo isso, a maquina ta começando a apresentar os sinais da idade até por conta que nem todo o conteudo do meu canal pode ser transmitido por Full Nvenc, quando eu uso o PS5 o Nvenc fica exclusivo para encodar a placa de captura para o OBS, consequencia que o nVENC fica travado e sou obrigado a usar o x264 (CPU) e também devo mirar o AV1 que está a caminho, então o ideal é que eventualmente eu terei de ter AV1 na GPU e na CPU.

O ponto crucial dessa curva, é que como to usando muito da minha maquina, estou colocando na balança de fazer um investimento pesado, para ganhar mais tempo no meu dia-a-dia.

No meu caso, partir logo pra um 7950X ou qualquer coisa agressiva desse ponto seria worth update?

:::Acho que postei em area errada:::, fiz a mesma pergunta numa area mais apropriada, my bad!:::

Última edição:

AMD Ryzen™ Chipset Driver Release Notes 4.11.15.342

Article Number

RN-RYZEN-CHIPSET-4-11-15-342

Release Highlights

- Bug fixes on few drivers

Known Issues

- Sometimes custom install fails to upgrade to latest drivers.

- Text alignment issues may be seen on Russian language.

- Manual system restart required on Non-English OS after the installation is complete.

- Uninstall summary log may incorrectly show uninstall status as fail on non-English OS.

Chipset Support

Processor Support

Package Contents

The AMD Ryzen™ Chipset Driver installation package contains various independent drivers designed to support the following Microsoft® Windows® platforms. Operating System support may vary depending on your specific AMD productAMD Ryzen™ Chipset Driver 4.11.15.342 installation package can be downloaded from the following link:

By clicking the Download button, you are confirming that you have read and agreed to be bound by the terms and conditions of the End User License Agreement (“EULA”). If you do not agree to the terms and conditions of these licenses, you do not have a license to any of the AMD software provided by this download.Installing AMD Ryzen Chipset Drivers

For detailed instructions on installing AMD Ryzen Chipset drivers, refer to the following article:Quase o preço que paguei no meu 5950x ano passado, tá bem bom7950x por R$4.200 na loja que explode

No futuro você colocará memória no PCI EXPRESS, pelo menos nos servidores

www.fabricatedknowledge.com

www.fabricatedknowledge.com

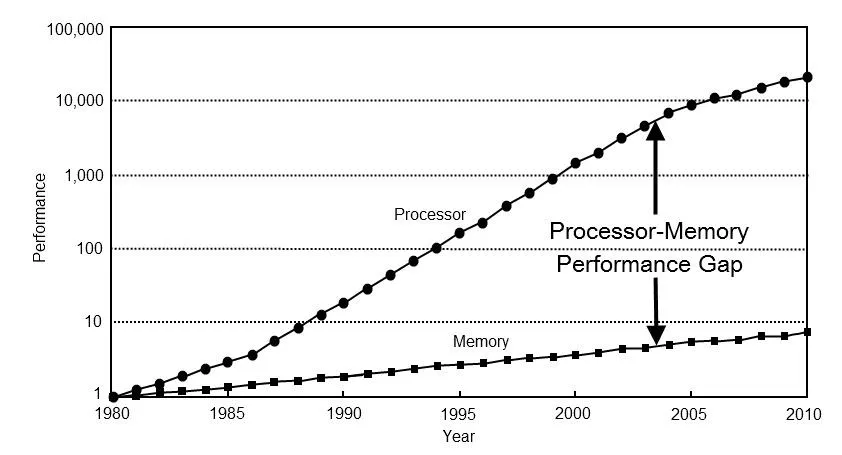

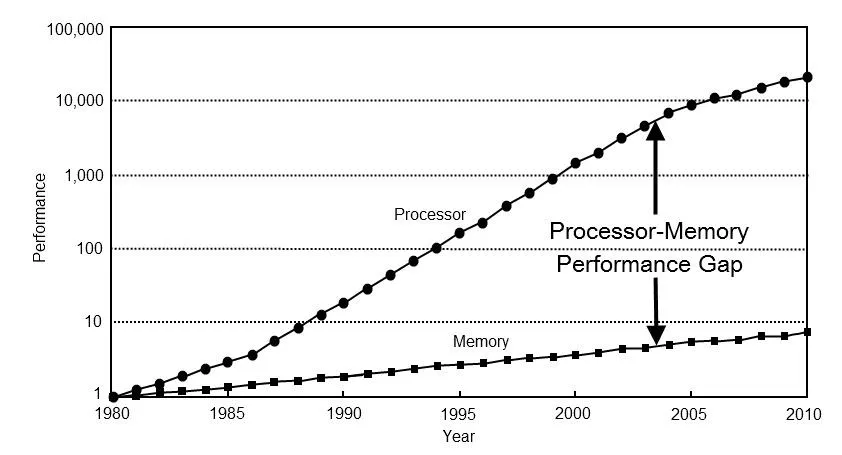

O gargalo é simples. No modelo Von Neumann de computação 1 , a estrutura padrão dos computadores atuais, um computador recebe informações da memória, processa-as e coloca a solução de volta na memória. O problema é que a busca de dados da memória para a CPU sempre foi mais lenta e, portanto, um gargalo. À medida que os processadores se tornaram mais rápidos, as taxas de memória não. Abaixo está um gráfico da lacuna de memória e processador.

CXL é um protocolo para conectar chips. É importante ressaltar que o CXL terá coerência e uma maneira de uma CPU ou acelerador se comunicar pela malha para falar com a memória fora de seu rack de servidor. Ao habilitar isso, você pode criar pools de computação, aceleração e memória, e tudo funcionará em uma grande matriz paralela. Esse é o sonho, pelo menos.

Estamos um pouco longe desse sonho, mas estamos começando o processo de algumas tecnologias-chave e capacitadores da topologia de data center mais provável no futuro. A parte crítica sobre a adoção do CXL é que a especificação 2.0 está efetivamente emparelhada com a especificação PCIe 5.0, e já que estamos prestes a começar a implantar o PCIe 5.0 no data center. Este é o início da curva de adoção do CXL.

CXL vem em três sabores diferentes; CXL.io, CXL.cache e CXL.memory. CXL.io é efetivamente PCIe 5.0, CXL.cache é focado em aceleradores capazes de acessar a memória em pool e CXL.memory é focado em oferecer configurações de memória em pool.

O FUTURO DA MEMÓRIA DO SISTEMA É PRINCIPALMENTE CXL

www.nextplatform.com

www.nextplatform.com

Como Omura aponta no gráfico acima, outro problema é que a contagem de núcleos nas CPUs está se expandindo mais rapidamente do que a largura de banda da memória; . E, finalmente, além de alguns projetos científicos, não há como agregar memória e mover a computação para mais perto dela para que possa ser processada no local, o que limita o desempenho geral dos sistemas. Gen Z da Hewlett Packard Enterprise, OpenCAPI da IBM e CCIX da Xilinx e do coletivo Arm eram todos candidatos a memória convergente e transporte de E/S, mas claramente o CXL da Intel emergiu como o padrão que todos seguirão em o longo prazo.

“O CXL está ganhando muita força e está trabalhando basicamente com todos os principais hiperescaladores em suas arquiteturas, ajudando-os a descobrir como implantarão essa tecnologia”, diz Omura. Daí a aquisição da Tanzanite, cujo valor não foi divulgado, que foi concluída no final de maio.

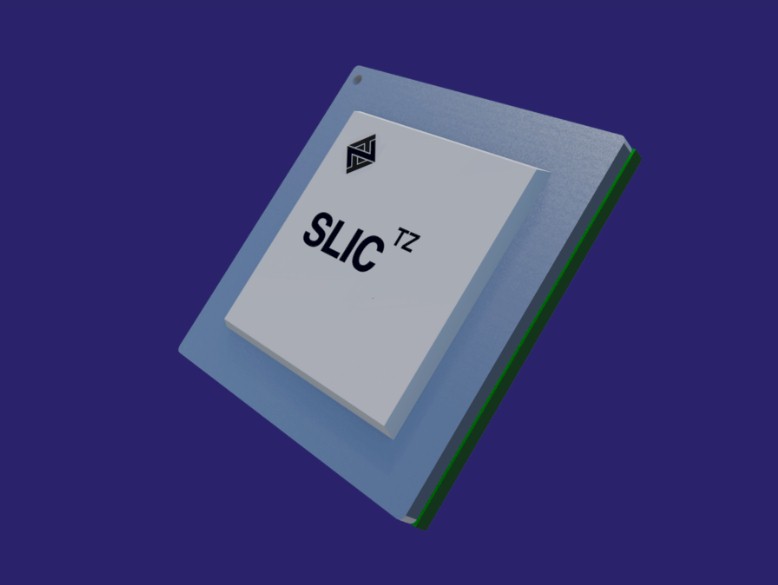

Com o chip SLIC, a Marvell poderá ajudar a indústria a criar fatores de forma DIMM padrão com controladores de expansão CXL, bem como módulos de memória expandida mais gordos e altos que são maiores que os fatores de forma DIMM. (A IBM fez o último com várias gerações de seus servidores Power Systems e seus "Centauros" caseiros: controladores de memória em buffer.)

A primeira coisa que a memória CXL fará é abrir a largura de banda da memória nos controladores DRAM e PCI-Express nos processadores modernos, diz Omura. E nós concordamos.

Se você tem um sistema hoje e tem uma largura de banda definida em seus slots de memória, pode aumentar a capacidade adicionando dois DIMMs por canal de memória, mas cada DIMM obtém metade da largura de banda de memória. Mas com a adição de DIMMs de memória CXL ao sistema usando o chip SLIC, você pode usar uma parte significativa do barramento PCI-Express para adicionar mais canais de memória ao sistema. É certo que a largura de banda que sai dos slots PCI-Express 5.0 não é tão alta e a latência não é tão baixa quanto com os controladores DRAM no chip, mas funciona. E em algum momento, quando o PCI-Express 6.0 estiver fora, pode não haver necessidade de controladores de memória DDR5 ou DDR6 em certas classes de processadores, e os controladores DDR podem se transformar em peças exóticas tanto quanto a memória empilhada HBM é exótica e apenas para especial casos de uso. A esperança para a memória CXL sobre PCI-Express 5.0 e 6. 0 não será muito pior (se for o caso) do que passar pelos links NUMA para um soquete adjacente em um sistema de vários soquetes, e pode ser ainda menos incômodo, uma vez que as portas CXL são literalmente as principais portas de memória em sistemas e DDR e HBM são as memórias especializadas e exóticas que são usadas apenas quando necessário. Pelo menos é o que pensamos que pode acontecer.

A expansão da memória CXL é apenas o primeiro estágio dessa evolução. Não demorará muito para que os chips CXL, como o SLIC da Marvell, sejam usados para criar pools de memória compartilhada em diversos – e muitas vezes incompatíveis – mecanismos de computação e, ainda mais adiante, podemos esperar que haja infraestrutura de comutação CXL que crie um malha combinável entre diferentes tipos de dispositivos de memória e diferentes tipos de mecanismos de computação. Assim:

E então, daqui a alguns anos, como já falamos várias vezes, teremos a verdadeira capacidade de composição dentro dos racks do datacenter, e não apenas para GPUs e flash trabalhando em PCI-Express. Mas em computação, memória e armazenamento de todos os tipos.

O que é CXL (e PCIe 5.0)

CXL: Protocol for Heterogenous Datacenters

Let's learn more about the world's most important manufactured product. Meaningful insight, timely analysis, and an occasional investment idea.

O gargalo é simples. No modelo Von Neumann de computação 1 , a estrutura padrão dos computadores atuais, um computador recebe informações da memória, processa-as e coloca a solução de volta na memória. O problema é que a busca de dados da memória para a CPU sempre foi mais lenta e, portanto, um gargalo. À medida que os processadores se tornaram mais rápidos, as taxas de memória não. Abaixo está um gráfico da lacuna de memória e processador.

CXL é um protocolo para conectar chips. É importante ressaltar que o CXL terá coerência e uma maneira de uma CPU ou acelerador se comunicar pela malha para falar com a memória fora de seu rack de servidor. Ao habilitar isso, você pode criar pools de computação, aceleração e memória, e tudo funcionará em uma grande matriz paralela. Esse é o sonho, pelo menos.

Estamos um pouco longe desse sonho, mas estamos começando o processo de algumas tecnologias-chave e capacitadores da topologia de data center mais provável no futuro. A parte crítica sobre a adoção do CXL é que a especificação 2.0 está efetivamente emparelhada com a especificação PCIe 5.0, e já que estamos prestes a começar a implantar o PCIe 5.0 no data center. Este é o início da curva de adoção do CXL.

CXL vem em três sabores diferentes; CXL.io, CXL.cache e CXL.memory. CXL.io é efetivamente PCIe 5.0, CXL.cache é focado em aceleradores capazes de acessar a memória em pool e CXL.memory é focado em oferecer configurações de memória em pool.

O FUTURO DA MEMÓRIA DO SISTEMA É PRINCIPALMENTE CXL

The Future Of System Memory Is Mostly CXL

What is the most expensive component that hyperscalers and cloud builders put into their X86 servers? It is the GPU accelerator, correct. So let’s ask

www.nextplatform.com

www.nextplatform.com

Como Omura aponta no gráfico acima, outro problema é que a contagem de núcleos nas CPUs está se expandindo mais rapidamente do que a largura de banda da memória; . E, finalmente, além de alguns projetos científicos, não há como agregar memória e mover a computação para mais perto dela para que possa ser processada no local, o que limita o desempenho geral dos sistemas. Gen Z da Hewlett Packard Enterprise, OpenCAPI da IBM e CCIX da Xilinx e do coletivo Arm eram todos candidatos a memória convergente e transporte de E/S, mas claramente o CXL da Intel emergiu como o padrão que todos seguirão em o longo prazo.

“O CXL está ganhando muita força e está trabalhando basicamente com todos os principais hiperescaladores em suas arquiteturas, ajudando-os a descobrir como implantarão essa tecnologia”, diz Omura. Daí a aquisição da Tanzanite, cujo valor não foi divulgado, que foi concluída no final de maio.

Com o chip SLIC, a Marvell poderá ajudar a indústria a criar fatores de forma DIMM padrão com controladores de expansão CXL, bem como módulos de memória expandida mais gordos e altos que são maiores que os fatores de forma DIMM. (A IBM fez o último com várias gerações de seus servidores Power Systems e seus "Centauros" caseiros: controladores de memória em buffer.)

A primeira coisa que a memória CXL fará é abrir a largura de banda da memória nos controladores DRAM e PCI-Express nos processadores modernos, diz Omura. E nós concordamos.

Se você tem um sistema hoje e tem uma largura de banda definida em seus slots de memória, pode aumentar a capacidade adicionando dois DIMMs por canal de memória, mas cada DIMM obtém metade da largura de banda de memória. Mas com a adição de DIMMs de memória CXL ao sistema usando o chip SLIC, você pode usar uma parte significativa do barramento PCI-Express para adicionar mais canais de memória ao sistema. É certo que a largura de banda que sai dos slots PCI-Express 5.0 não é tão alta e a latência não é tão baixa quanto com os controladores DRAM no chip, mas funciona. E em algum momento, quando o PCI-Express 6.0 estiver fora, pode não haver necessidade de controladores de memória DDR5 ou DDR6 em certas classes de processadores, e os controladores DDR podem se transformar em peças exóticas tanto quanto a memória empilhada HBM é exótica e apenas para especial casos de uso. A esperança para a memória CXL sobre PCI-Express 5.0 e 6. 0 não será muito pior (se for o caso) do que passar pelos links NUMA para um soquete adjacente em um sistema de vários soquetes, e pode ser ainda menos incômodo, uma vez que as portas CXL são literalmente as principais portas de memória em sistemas e DDR e HBM são as memórias especializadas e exóticas que são usadas apenas quando necessário. Pelo menos é o que pensamos que pode acontecer.

A expansão da memória CXL é apenas o primeiro estágio dessa evolução. Não demorará muito para que os chips CXL, como o SLIC da Marvell, sejam usados para criar pools de memória compartilhada em diversos – e muitas vezes incompatíveis – mecanismos de computação e, ainda mais adiante, podemos esperar que haja infraestrutura de comutação CXL que crie um malha combinável entre diferentes tipos de dispositivos de memória e diferentes tipos de mecanismos de computação. Assim:

E então, daqui a alguns anos, como já falamos várias vezes, teremos a verdadeira capacidade de composição dentro dos racks do datacenter, e não apenas para GPUs e flash trabalhando em PCI-Express. Mas em computação, memória e armazenamento de todos os tipos.

AMD Ryzen 7000 obtém cortes de preço significativos na loja virtual oficial

A AMD agora implementou os mesmos preços para suas CPUs de desktop Zen4 como Newegg e Amazon em sua própria loja oficial nos EUA.

A empresa agora seguiu outros grandes varejistas que foram os primeiros a oferecer a série Ryzen 7000 para desktop a preços significativamente mais baixos. O desconto se aplica a todos os quatro SKUs Ryzen 7000 lançados há menos de dois meses.

O que é interessante sobre a própria oferta da AMD é que o desconto é mostrado como “Novo Preço Baixo”, embora a loja de produtos também mencione “Pre-Black Friday Deals”. Ainda assim, em vez de dizer “preço mais baixo”, os consumidores são informados de que são novos preços. Portanto, podemos assumir que este é um corte de preço permanente na série Ryzen 7000.

A AMD descontou as CPUs de desktop Zen4 em até US$ 125 (7950X). Este é um grande desconto para a mais recente série de processadores da AMD, geralmente não visto tão cedo após o lançamento do produto. No entanto, a AMD está lutando para vender o estoque principalmente devido aos preços muito altos das placas-mãe AMD AM5, necessárias para o Ryzen 7000.

Amazon EUA:

Loja virtual oficial da AMD:

Todos os quatro processadores parecem estar em estoque em todos os varejistas que verificamos. Parece que a AMD está tentando aumentar o estoque antes que a Intel abandone sua série não-K de 13ª geração em janeiro. No entanto, a AMD também deve apresentar até três novos processadores não -x no próximo ano. Uma coisa é clara, quanto mais CPUs estiverem disponíveis, mais difícil será vender os modelos premium.

Fonte: AMD

Com essa queda de preços, estou tentado a pegar um 7900x.... O que tá matando e o preço das motherboards... 6k a x670e hero..

Tinha pago 550 dólares no 7900x sábado.

Ai domingo caiu pra 475

Como minha amiga que buscou não quis dar o trabalho pra ela de dar return.

Ai hoje abri o chat na microcenter expliquei pra eles que o preço caiu bla bla e ele vao estornar os 75 dólares a mais.

Ou seja 7900x a 475 dólares com a memoria de graça.

Eu:

Last week I bought a combo at Microcenter, but two days later, Ryzen received a price cut, but my product was at the old price, to get the new price would I have to return the product and buy again?

Adam (atendente)

Ok you should get that refunded to you in the next 5-7 business days

Eu:

What the exactly value of the refund?

Adam

$51

Era pra ser 75 mas eu tinha um cupom de 25 ai ele só consegue dar a diferença.

Isso sem burocracia nenhuma, outro patamar.

Ai domingo caiu pra 475

Como minha amiga que buscou não quis dar o trabalho pra ela de dar return.

Ai hoje abri o chat na microcenter expliquei pra eles que o preço caiu bla bla e ele vao estornar os 75 dólares a mais.

Ou seja 7900x a 475 dólares com a memoria de graça.

Eu:

Last week I bought a combo at Microcenter, but two days later, Ryzen received a price cut, but my product was at the old price, to get the new price would I have to return the product and buy again?

Adam (atendente)

Ok you should get that refunded to you in the next 5-7 business days

Eu:

What the exactly value of the refund?

Adam

$51

Era pra ser 75 mas eu tinha um cupom de 25 ai ele só consegue dar a diferença.

Isso sem burocracia nenhuma, outro patamar.

Tinha pago 550 dólares no 7900x sábado.

Ai domingo caiu pra 475

Como minha amiga que buscou não quis dar o trabalho pra ela de dar return.

Ai hoje abri o chat na microcenter expliquei pra eles que o preço caiu bla bla e ele vao estornar os 75 dólares a mais.

Ou seja 7900x a 475 dólares com a memoria de graça.

Eu:

Last week I bought a combo at Microcenter, but two days later, Ryzen received a price cut, but my product was at the old price, to get the new price would I have to return the product and buy again?

Adam (atendente)

Ok you should get that refunded to you in the next 5-7 business days

Eu:

What the exactly value of the refund?

Adam

$51

Era pra ser 75 mas eu tinha um cupom de 25 ai ele só consegue dar a diferença.

Isso sem burocracia nenhuma, outro patamar.

Claro né...

A chance de voce voltar é mto maior fazendo desta forma.

Eu tb acho.Claro né...

A chance de voce voltar é mto maior fazendo desta forma.

Mas em paralelo a essa conversa tava tentando resolver um problema na Kabum e o cara falou "tem que esperar a resposta por email" mesmo eles não respondendo o email.

Não vejo necessidade de uma placa x670e top das galaxias.Com essa queda de preços, estou tentado a pegar um 7900x.... O que tá matando e o preço das motherboards... 6k a x670e hero..

Peguei um Steel Legend da Asrock por 2300 no brasil com NF. Pra mim ta de boas.

Loja que Explode, do Pombo e Mil Gigas são oto pata mar.Eu tb acho.

Mas em paralelo a essa conversa tava tentando resolver um problema na Kabum e o cara falou "tem que esperar a resposta por email" mesmo eles não respondendo o email.

Essas citados só se coçam de verdade depois do procon/reclameaqui/consumidor.gov até lá só tentar enrolar o cidadãoLoja que Explode, do Pombo e Mil Gigas são oto pata mar.

É que eu quero as firulas da Asus nessa gen. Sem falar que vou ficar até o final da gen com a placa. Pior que nem a Strix têm em estoque.Não vejo necessidade de uma placa x670e top das galaxias.

Peguei um Steel Legend da Asrock por 2300 no brasil com NF. Pra mim ta de boas.

--- Post duplo é unido automaticamente: ---

Alguém sabe dizer se essas ddr5 6000mhz, têm muita diferença de cl 40 para 30 ou 32?

Users who are viewing this thread

Total: 1 (membros: 0, visitantes: 1)