Nunca testei limitar pela temperatura mas é uma boa mesmo, mais simples que pedir pro povo mexer em PBO com PPT/TDC/EDC, fazer CO arriscando estabilidade e os krl, e ainda dá pra setar exatamente na temperatura máxima que cada um acha melhor, vou passar a recomendar isso agora kkkkPutz, passando só p relatar que depois de um tempão finalmente achei a parada de limitar o 7700x pela temperatura.

setei 70 graus Level 3 e pelos testes simples do cpuz, antes chegando a 99,4 gastava 104w, agora com 70 ta gastando 82w com 4% de diferença de desempenho!

agora vou acertar as curvas do master liquid pra ver se melhora

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

[TÓPICO DEDICADO] AMD Ryzen Socket AM5 - Zen 4, Zen 5 e além

- Iniciador de Tópicos Morello

- Data de Início

Baita diferença pra pouca perda e consumindo até menos que o meu 7900.Putz, passando só p relatar que depois de um tempão finalmente achei a parada de limitar o 7700x pela temperatura.

setei 70 graus Level 3 e pelos testes simples do cpuz, antes chegando a 99,4 gastava 104w, agora com 70 ta gastando 82w com 4% de diferença de desempenho!

agora vou acertar as curvas do master liquid pra ver se melhora

Tá com gigabyte né? O ajuste de fábrica dos fans é muito agressivo até no perfil silent, tive que fazer manualmente, avançar os sliders e levei um tempo até deixar redondo mas hoje só escuto os fans se a temperatura ambiente estiver na casa dos 30+ºC, ainda assim eles não ficam na rotação máxima e as temperaturas dos componentes ficam ótimas.

Não conheço seu WC e não há receita de bolo pra isso mas se quiser colar:

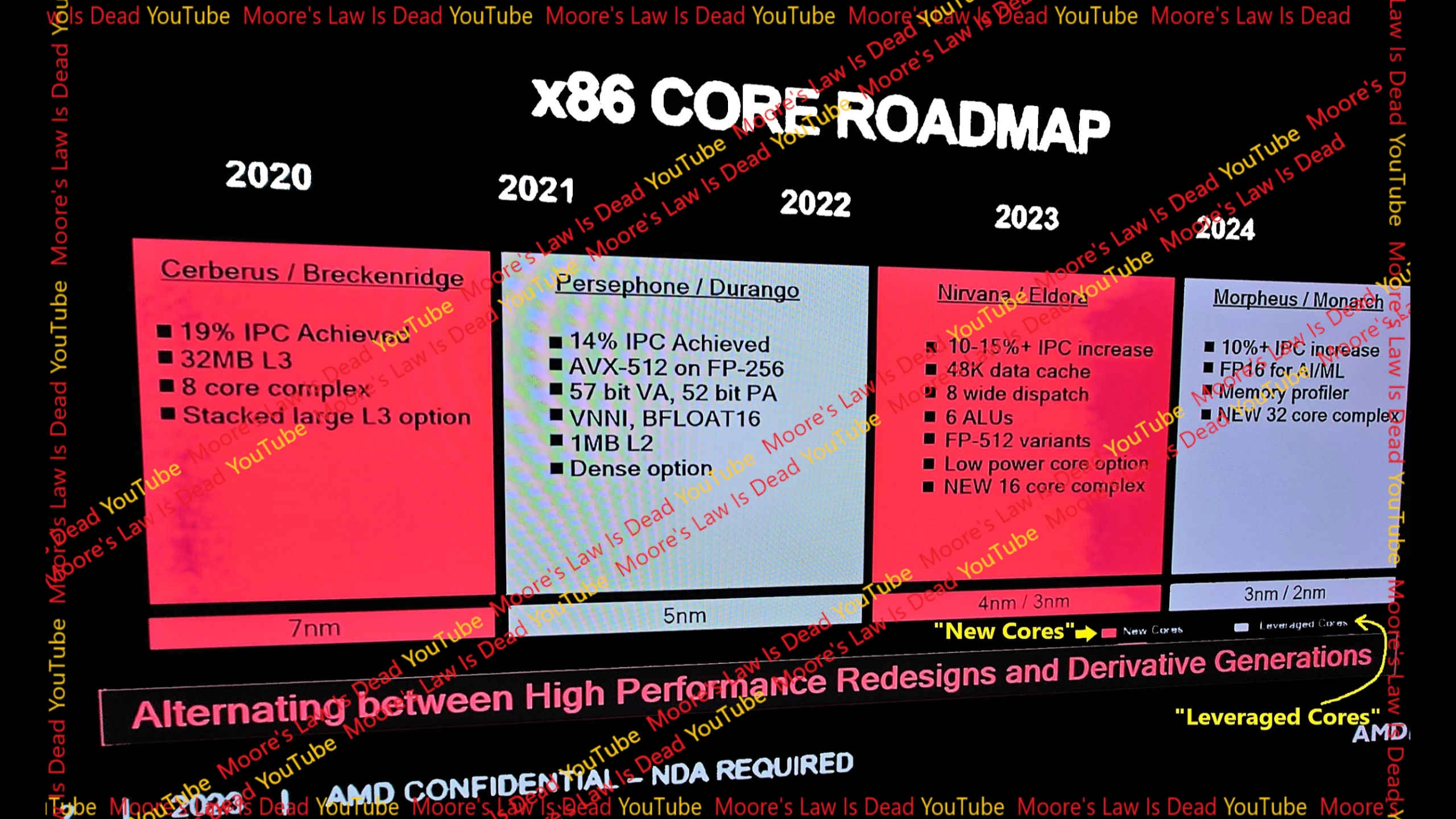

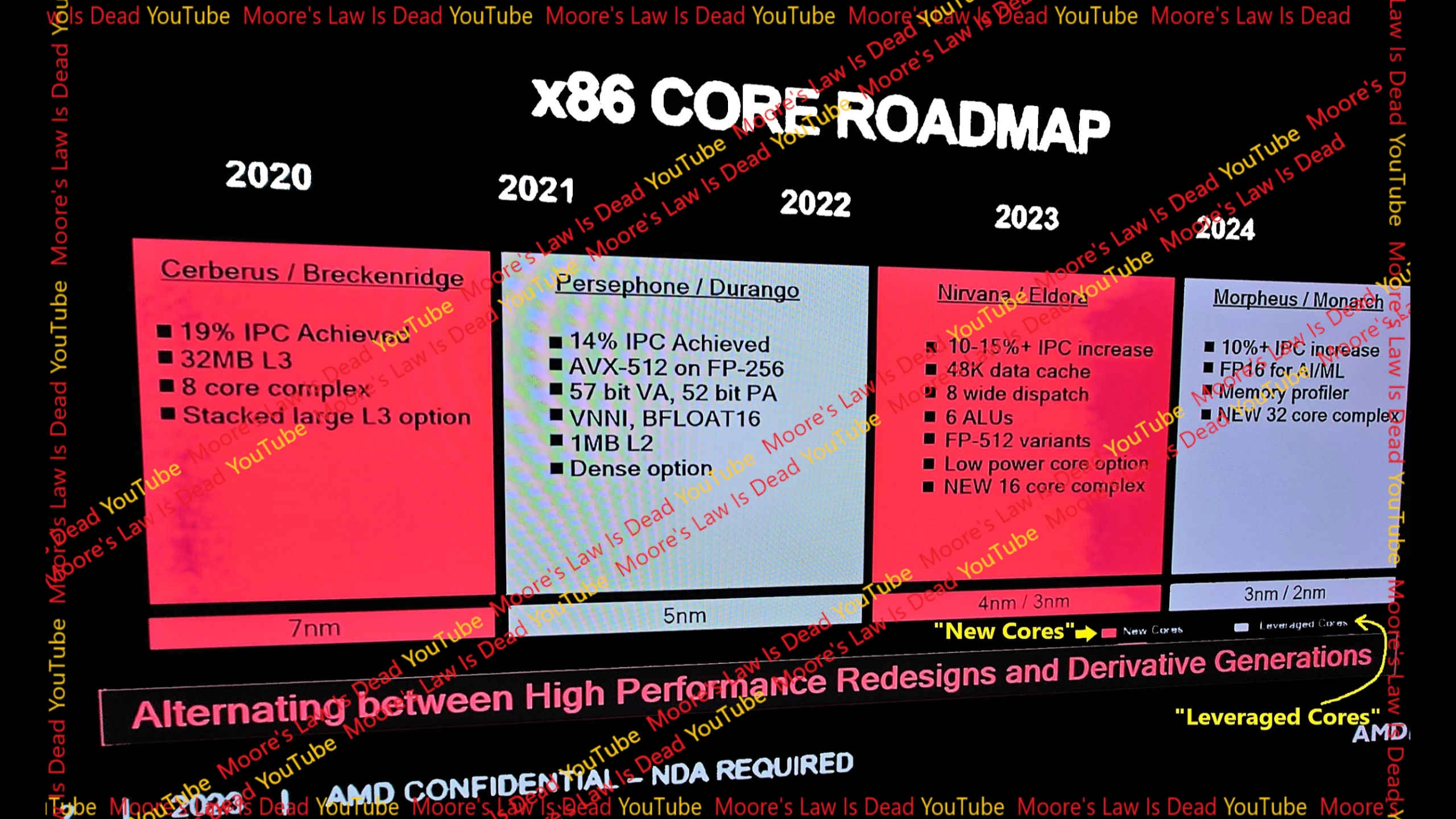

Vazamento do roteiro do núcleo AMD x86, microarquiteturas Zen5 (Nirvana) Zen6 (Morpheus) detalhadas

Detalhes do AMD Zen5 e Zen6 vazam

Um novo vazamento acaba de ser compartilhado pelo canal Moore’s Law is Dead .

AMD x86 core roadmap leaks out, Zen5 (Nirvana) Zen6 (Morpheus) microarchitectures detailed - VideoCardz.com

AMD Zen5 and Zen6 details leak out A new leak has just been shared by Moore’s Law is Dead channel. AMD x86 Core Roadmap, Source: Moore’s Law is Dead The YouTuber has shared two slides extracted from an AMD internal presentation, originally not intended for public consumption. These slides...

Roteiro do núcleo AMD x86, fonte: A lei de Moore está morta

O YouTuber compartilhou dois slides extraídos de uma apresentação interna da AMD, originalmente não destinada ao consumo público. Esses slides fornecem uma atualização sobre o progresso e as estratégias relativas às futuras arquiteturas Zen da próxima geração, revelando alguns detalhes fundamentais, como melhorias antecipadas de IPC, recursos suportados e contagens principais.

O roteiro parece ter sofrido um pequeno ajuste temporal. No entanto, é crucial ter em mente que estas microarquitecturas abrangem uma vasta gama de produtos, abrangendo tanto data centers como séries orientadas para o consumidor. Como resultado, os cronogramas de lançamento podem não refletir exclusivamente as intenções da AMD para Ryzen 8000 e além, mas também abranger considerações para produtos EPYC.

Nirvana Zen5 (1º semestre de 2024)

As novas microarquiteturas de 4nm/3nm descritas incluem Nirvana (Zen5), que se destina à série Ryzen 8000. De acordo com o slide, a expectativa é de aumento do IPC de 10 a 15%. O IPC ainda pode aumentar, pois a apresentação mostra apenas uma meta que ainda não foi verificada pelo varejo de silício. Além disso, o slide lista cache de dados de 48K, 8 despachos amplos, 6 ALUs, variantes FP-512 e uma nova opção de núcleo de baixo consumo de energia.

O mais interessante é que oferece um complexo de 16 núcleos. Este último é provavelmente uma opção usando exclusivamente variantes Zen5c. Como lembrete, a APU Strix Point usará ambas as subarquiteturas dentro de um único dado. Em outras palavras, os jogadores na plataforma AM5 devem esperar designs Zen5 de até 16 núcleos ou Zen5c de 32 núcleos, ou uma mistura de ambos, caso a AMD siga esse caminho (como 8x Zen5 + 16x Zen5c).

AMD Nirvana (Zen5), Fonte: A Lei de Moore está morta

Morfeu Zen6 (2H 2025)

O Morpheus é o codinome da microarquitetura Zen6. Espera-se agora que use tecnologia de processo de 3nm e 2nm, e a AMD tem como meta atingir um aumento de 10% no IPC em relação ao Nirvana. A AMD está planejando introduzir instruções FP16 para aceleração de algoritmos AI/ML e um novo perfilador de memória. Em termos de complexidade de núcleos, a AMD está aumentando a contagem de núcleos para 32, o que novamente deve se referir ao Zen6c, não ao Zen6.

Diz-se que a microarquitetura Zen6 oferece um redesenho de layout de chip semelhante ao Zen2 com novas técnicas de empacotamento, afirma o MLID. Embora não esteja confirmado, é mencionado que para Zen6 a AMD pode empilhar CCDs em cima do IOD (matriz de interface de entrada/saída). Esta seria uma grande mudança na abordagem desagregada de design de chips da AMD para empilhamento de matrizes. O que falta confirmar é se o Zen6 vai usar o soquete AM5.

Boa noite pessoal!

Adquiri algumas peças (Ryzen 7 7800x3d, G.Skill 6000, NVMe WD850X) nos EUA no início do mês e, ao chegar aqui, comprei o restante. Estou enfrentando problemas com a placa mãe. A primeira que comprei, a MSI PRO B650-P, tive que devolver porque não era compatível com o gabinete Thermaltake P6 Core, já que o shield dela não era fixo, deixando o gabinete desprotegido. Fiz a devolução e comprei outra na KABUM, a TUF B650 WIFI OPENBOX. No entanto, essa placa veio com alguns pinos do socket desalinhados, mas funcionou. O problema é que os slots 1 e 3 das memórias não estão funcionando, apenas os slots 2 e 4. Já solicitei a devolução hoje e tenho dois reembolsos pendentes na KABUM.

Ao pesquisar sobre o assunto no tópico de AM5, descobri que esse processador está apresentando alguns problemas de compatibilidade com memória.

Estou considerando a possibilidade de adquirir uma placa mãe um pouco melhor, como a ASROCK B650-E STEAL LEGEND ou a ASUS X670-E TUF, e até mesmo a ASUS X670-E PRIME. Vocês poderiam me ajudar com informações sobre essas placas-mãe ou se tem uma melhor na mesma faixa de preço?

Observação: Consegui resgatar Starfield a tempo, não conhecia esse tipo de resgate que pede aplicativo para verificar o processador, já sou da velha guarda.

Essa questão da Mobo nao pegar o Slot 1 e 3, todas as asus que testei (2 Prime X670-e , e 2 TUF X670-e) elas tem esse comportamento por causa do alto Mhz das memorias.

Comprei 2x32gb 6000mhz da Corsair, e nos slots 1 e 3 só funcionam se eu baixar o clock delas, até comprei mais dois pentes do mesmo modelo para ficar com 128gb, e ficou bem instavel, demorando muito para bootar, e isso quando bootava, acabei desistindo e ficando só com 2x32 mesmo.

Se olhar nos foruns da Asus tem um monte de gente reclamando desse funcionamento das placas, provavelmente alguma coisa relacionada a Bios e a AGESA, porque algumas atualizações pioraram a estabildade com 128gb.

128gb só veio ficar estável em bios mais recentes, mas mesmo assim acho que ainda não rola 6000MHz. Fun fact: 192gb (4x48gb) aparenta ser mais estável que 128gbEssa questão da Mobo nao pegar o Slot 1 e 3, todas as asus que testei (2 Prime X670-e , e 2 TUF X670-e) elas tem esse comportamento por causa do alto Mhz das memorias.

Comprei 2x32gb 6000mhz da Corsair, e nos slots 1 e 3 só funcionam se eu baixar o clock delas, até comprei mais dois pentes do mesmo modelo para ficar com 128gb, e ficou bem instavel, demorando muito para bootar, e isso quando bootava, acabei desistindo e ficando só com 2x32 mesmo.

Se olhar nos foruns da Asus tem um monte de gente reclamando desse funcionamento das placas, provavelmente alguma coisa relacionada a Bios e a AGESA, porque algumas atualizações pioraram a estabildade com 128gb.

Sim, quando tava testando vi uma galera colocando na base (3600mhz) para rodar com 128gb.128gb só veio ficar estável em bios mais recentes, mas mesmo assim acho que ainda não rola 6000MHz. Fun fact: 192gb (4x48gb) aparenta ser mais estável que 128gb

Percebi que esses 192gb estão mais estaveis, mas não achei para vender esses pentes ainda. Lá no site da asus realmente tem mais pentes 4x48 certificados do que 4x32, uma loucura.

Sim, nem pra europa tem os pentes de 48gb fácil pra achar, só em alguns lugares dos USSim, quando tava testando vi uma galera colocando na base (3600mhz) para rodar com 128gb.

Percebi que esses 192gb estão mais estaveis, mas não achei para vender esses pentes ainda. Lá no site da asus realmente tem mais pentes 4x48 certificados do que 4x32, uma loucura.

Com bios mais recentes o pessoal tá conseguindo 128gb em 5200~5600MHz mais tranquilo.

tem a questão da impedância e outros ajustes de sinal, sem um refinamento a DDR5 não vai atingir seu potencial plenoEssa questão da Mobo nao pegar o Slot 1 e 3, todas as asus que testei (2 Prime X670-e , e 2 TUF X670-e) elas tem esse comportamento por causa do alto Mhz das memorias.

Comprei 2x32gb 6000mhz da Corsair, e nos slots 1 e 3 só funcionam se eu baixar o clock delas, até comprei mais dois pentes do mesmo modelo para ficar com 128gb, e ficou bem instavel, demorando muito para bootar, e isso quando bootava, acabei desistindo e ficando só com 2x32 mesmo.

Se olhar nos foruns da Asus tem um monte de gente reclamando desse funcionamento das placas, provavelmente alguma coisa relacionada a Bios e a AGESA, porque algumas atualizações pioraram a estabildade com 128gb.

e tb tem a ver com a densidade desses módulos no arranjo. Não sei exatamente o motivo dos 48GB funcionar melhor, mas pode ser por semelhança com os de 16GB que funcionam bem enquanto os de 32GB podem ter dificuldades, mesmo sendo EXPO128gb só veio ficar estável em bios mais recentes, mas mesmo assim acho que ainda não rola 6000MHz. Fun fact: 192gb (4x48gb) aparenta ser mais estável que 128gb

já vi postarem 6000MHz com 128GB, não lembro se era EXPOSim, nem pra europa tem os pentes de 48gb fácil pra achar, só em alguns lugares dos US

Com bios mais recentes o pessoal tá conseguindo 128gb em 5200~5600MHz mais tranquilo.

48GB é mais denso que os de 32GB (16 vs 32 é a mesma coisa de 24 vs 48gb). Acho que talvez os módulos estejam em um processo mais maduro? Ninguém parece saber ao certo, só sabem que é mais estável kkkkke tb tem a ver com a densidade desses módulos no arranjo. Não sei exatamente o motivo dos 48GB funcionar melhor, mas pode ser por semelhança com os de 16GB que funcionam bem enquanto os de 32GB podem ter dificuldades, mesmo sendo EXPO

Ah, verdade, mas não acho que era EXPO:já vi postarem 6000MHz com 128GB, não lembro se era EXPO

DDR5 4 dimms on am5 -- what's working, what's not?

Confirmed. With AGESA 1.0.0.7c, I can run 6000 stable now.

forum.level1techs.com

forum.level1techs.com

Depende do seu CPU, sua GPU, sua resolução, o jogo, quais settings tá usando no jogo etcetc, falta muita informação pra poder falar qualquer coisaPessoal, minhas ddr5 sao da asgard freyr 5200...

como um tiro de misericordia no ALI, to pensando em pegar o kit 6400mhz de mesmo modelo, PRA DEPOIS vender o kit atual

vale a pena? da muita diferença no desempenho?

Pessoal, minhas ddr5 sao da asgard freyr 5200...

como um tiro de misericordia no ALI, to pensando em pegar o kit 6400mhz de mesmo modelo, PRA DEPOIS vender o kit atual

vale a pena? da muita diferença no desempenho?

A AMD vendeu no lançamento a ideia de que 6000MTs era o Sweet Spot, após o AGESA 1.0.0.7c não sei se isso ainda está valendo, pois pelo que tenho - pouco - acompanhado o pessoal tem conseguido atingir frequências ainda maiores. De qualquer forma, no caso da AMD os Ryzen se beneficiam mais de latências menores do que frequências maiores, então se a ideia é ter o máximo desempenho atente-se as latências dos kits.

Outra coisa também, dê uma olhada nas lojas nacionais e no Mercado Livre, esses dias consegui um Kit 32GB (2x16) Trident Z5 6400MTs CL32 XMP lacrado por 890 reais no Mercado Livre, peguei ele pra combar com um 13600K que tenho (e quem sabe com um futuro 14600K). As memórias EXPO eram bem escassas até alguns meses (continuam escassas nas lojas), mas percebi que no Mercado Livre você as acha com facilidade, enfim, na dúvida particularmente procuraria um Kit EXPO 6000MTs CL30.

Última edição:

Foi malz...Depende do seu CPU, sua GPU, sua resolução, o jogo, quais settings tá usando no jogo etcetc, falta muita informação pra poder falar qualquer coisa

Ryzen 7700x, 32gb, 5700xt (aguardando uma 3080).

Até que jogo uma coisa ou outra bem leve em ultrawide 1080p, mas tenho usado o pc mais pra converter videos, upscalling via IA etc.

A compra de agora, seria p não ter q mexer futuramente (que os preços prometem escalar absurdamente)

Última edição:

Com uma 3080 eu acho que nem me incomodaria com isso, em 1080p UW pode ser que tenha ganho em alguns jogos sim mas só testando pra saber, um jogo pode dar, outro não e por aí vai, pra produtividade creio que não mude nada ou pouca coisa no geral, e preços subirem absurdamente pelos impostos no Ali você diz? Possível mas acho que os preços DDR5 aqui tão até aceitáveis considerando que ainda é algo novo e devem baixar no futuro ainda, quando montei o 2° PC aqui de casa 2x8gb 2400mhz era uns 500-600 conto e agora tem 2x16gb 3200 por menos que isso as vezes por exemplo, mas pra deixar alguns exemplos de diferença de memória aí, só que vai ser tudo numa 4090 em 1080pFoi malz...

Ryzen 7700x, 32gb, 5700xt (aguardando uma 3080).

Até que jogo uma coisa ou outra bem leve em ultrawide 1080p, mas tenho usado o pc mais pra converter videos, upscalling via IA etc.

A compra de agora, seria p não ter q mexer futuramente (que os preços prometem escalar absurdamente)

AMD Ryzen 7000 Series [Zen 4] RAM/Memory Scaling feat. Tuned Memory - RYZEN 7700X

Ryzen 9 7950X3D Memory Scaling Benchmark, Does DDR5 Performance Matter?

Até onde sei é 100% compatível sim, e eu usaria sem medo, tem gente usando até AG400 nele e dar conta é bem subjetivo, tem gente que não pode ver passar de 70c, outros 75c, outros 80c mas tecnicamente tudo isso é dar conta, fora a variação de temp ambiente e gabinete, as vezes uma pessoa num AG400 com temp ambiente boa e gabinete bom tem temp melhor que alguém num NH-D15 ou AIO 240m/360mmOs cooler do AM4 encaixam de boa no AM5 ?

Tenho um Mugen5 rev b, estava pensando em pegar um 7800x3d, será que da conta?

Decidi que vou pegar um 7800x3d + B650m Tuf + Ddr5 chip a-die 6400mt/s Hinyx Kingbank ou Juhor, devo me preocupar com essas memórias na placa da Asus ou funciona legal? Acham que a combinação ficou ok? A Asus é uma boa ou gasto mais em uma Aorus Elite ax?

Última edição:

Nada de preocupação e vai funcionar muito bem na mobo da Asus, kit excelente e vai dar mais performance principalmente em jogos!Decidi que vou pegar um 7800x3d + B650m Tuf + Ddr5 chip a-die Hinyx Kingbank ou Juhor, devo me preocupar com essas memórias na placa da Asus ou funciona legal? Acham que a combinação ficou ok? A Asus é uma boa ou gastto mais em uma Aorus Elite ax?

Terá , mas hoje você sente falta de algum jogo que o seu sistema atual esta deixando a desejar? Porque nesse resolução o seu kit atual deve empurrar a maioria dos jogos.Pois é, mas estou pensando se vou ter algum ganho, atualmente jogo em 1440p com a 4070TI + 5800x3d. A ideia é vender o kit atual para abater um pouco o valor e up sairá por volta de uns R$1500. Uma boa ideia será?

Não, por enquanto está me atendendo super bem, seria pensando em aproveitar o momento antes do remessa conforme e preparar o terreno para as novas Nvidia ano que vem.Terá , mas hoje você sente falta de algum jogo que o seu sistema atual esta deixando a desejar? Porque nesse resolução o seu kit atual deve empurrar a maioria dos jogos.

Certo, se tu tem a grana pra investir vai fundo e fica esperando a próxima geração da Nvidia é sempre bom ficar atualizadoNão, por enquanto está me atendendo super bem, seria pensando em aproveitar o momento antes do remessa conforme e preparar o terreno para as novas Nvidia ano que vem.

Até onde sei é 100% compatível sim, e eu usaria sem medo, tem gente usando até AG400 nele e dar conta é bem subjetivo, tem gente que não pode ver passar de 70c, outros 75c, outros 80c mas tecnicamente tudo isso é dar conta, fora a variação de temp ambiente e gabinete, as vezes uma pessoa num AG400 com temp ambiente boa e gabinete bom tem temp melhor que alguém num NH-D15 ou AIO 240m/360mm

Por mim não dando thermal throttling ta de boa. Independente da temperatura.

Dependendo do caso acho válido, se a CPU estiver segurando a GPU teria um ganho imediato e vai ter mais folga no futuro pra uma GPU melhor, mas vai muito do que você acha da sua performance atual e qual GPU pretende botar futuramente também, é complicado dizer exatamente se vai ter algum ganho porque é muito único de cada jogo, settings que cada um usa etc, eu to com uma 4080 pra 3840x1600/3840x1080 por exemplo e uma CPU melhor não mudaria minha vida na maioria do que tenho jogado, tanto que uso o CPU com clock base de 3,7ghz e o desempenho continua igual nas médias, agora se eu jogasse alguns jogos mais exigentes de CPU eu poderia ter um ganho de 10-20%, e daí do 5800x pro 5800x3D mais uns 10-20% etcPois é, mas estou pensando se vou ter algum ganho, atualmente jogo em 1440p com a 4070TI + 5800x3d. A ideia é vender o kit atual para abater um pouco o valor e up sairá por volta de uns R$1500. Uma boa ideia será?

Nesse caso acho que vai com folga mesmo rodando stock, no geral vejo temperaturas menores no 7800x3D que no 5800x3DPor mim não dando thermal throttling ta de boa. Independente da temperatura.

Salve a todos!!

Avaliando o upgrade aqui, saindo de um kit Intel i5 8600k @4.7ghz+ 16gb 3600mhz + RTX 3070, vou migrar para am5.

A duvida é: economizar com processador, pegar um Ryzen 7600 considerando que já é um baita processador, e um bom upgrade pro i5 8600k;

ou

gastar um pouco mais (R$1,2/2k a mais no kit) e meter a cara num 7800x3d?

O upgrade será composto por processador Ryzen + mobo B650 + 32gb 6000mhz CL32 ou 36

Vou continuar com algumas peças por hora, como, wc Cougar Aqua 240mm, gabinete Corsair 600T, RTX 3070 (4080 no futuro), monitor Dell 34" 1440p ultra wide 144hz.

Me parece 8 ou 80, mas a diferença de preço x performance não ficou muito claro pra mim. Em alguns testes o 7600 não fica tão pra trás de um 7800x3d, pelo menos nada que valha pagar a diferença, e o outros processadores intermediários não me chamam atenção.

Ajuda ai, vlw!!

Avaliando o upgrade aqui, saindo de um kit Intel i5 8600k @4.7ghz+ 16gb 3600mhz + RTX 3070, vou migrar para am5.

A duvida é: economizar com processador, pegar um Ryzen 7600 considerando que já é um baita processador, e um bom upgrade pro i5 8600k;

ou

gastar um pouco mais (R$1,2/2k a mais no kit) e meter a cara num 7800x3d?

O upgrade será composto por processador Ryzen + mobo B650 + 32gb 6000mhz CL32 ou 36

Vou continuar com algumas peças por hora, como, wc Cougar Aqua 240mm, gabinete Corsair 600T, RTX 3070 (4080 no futuro), monitor Dell 34" 1440p ultra wide 144hz.

Me parece 8 ou 80, mas a diferença de preço x performance não ficou muito claro pra mim. Em alguns testes o 7600 não fica tão pra trás de um 7800x3d, pelo menos nada que valha pagar a diferença, e o outros processadores intermediários não me chamam atenção.

Ajuda ai, vlw!!

Users who are viewing this thread

Total: 2 (membros: 0, visitantes: 2)