Talvez o scaling não seja exatamente o mesmo pra Intel, e poderia tentar tunar manualmente o seu kit pra ver no que dá, não sei como tá isso nas DDR5 mas nas DDR4 tem kits 3000 CL15/3200 CL16 que sobem pra 4000 CL16 (geralmente o processador que limita no caso dos Ryzen) e dá pra apertar vários subtimings, o ideal é sempre fazer tudo manualmente pra ter o melhor do melhor de qualquer forma, mesmo comprando Samsung B-die (no caso das DDR4)Cara... 10 FPS é MUITA COISA.

Minha DDR5 é 5200...

To falando dessa primeira (de cima pra baixo)... to achando estranho isso...

To pensando em pegar G.Skill 6400 e sair dessa minha 5200.... 10 FPS velho???

Vocês não estão achando estranho não?

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

[TÓPICO DEDICADO] NAVI - próxima geração de GPUs da AMD

- Iniciador de Tópicos brender

- Data de Início

Tem esse teste por aí com o 13900K?

Nunca pesquisei sobre..hehe

mas geralmente intel dá menos diferença..

Talvez o scaling não seja exatamente o mesmo pra Intel, e poderia tentar tunar manualmente o seu kit pra ver no que dá, não sei como tá isso nas DDR5 mas nas DDR4 tem kits 3000 CL15/3200 CL16 que sobem pra 4000 CL16 (geralmente o processador que limita no caso dos Ryzen) e dá pra apertar vários subtimings, o ideal é sempre fazer tudo manualmente pra ter o melhor do melhor de qualquer forma, mesmo comprando Samsung B-die (no caso das DDR4)

edie sobe mto tb...

aqui fiz 3000@3800cl16..

19% minimos

15,8% avg

Acabei de desistir de trocar meu 5600 por 5800x3D..

Investir +200% pra ter 17% de volta...no way

Ainda mais que a minha C1 é 120hz mesmo..

Mas pra 4K nem vale a pena mesmo. Seria pra 1440p e olha lá...

Uso as mesmas aqui, 3000 CL15 @3733 CL16 porque o 5800x não deu boot quando botei 1900mhz 1:1 aí nem quis fuçar mas reduzi alguns subtimings depois, acho que é até mais importante mexer nos subtimings que só a frequência e o tCL e timings primários, mas mexer em RAM é chato pra krl kkkkkk, e agora como migrei pra 4k também não faz mais sentido bater cabeça com isso com a GPU atualedie sobe mto tb...

aqui fiz 3000@3800cl16..

Mas pra 4K nem vale a pena mesmo. Seria pra 1440p e olha lá...

Pra 4090 faz diferença até em 4k, mas depende mto do jogo..

1440p dá bastante diferença em alguns casos..srr

Uso as mesmas aqui, 3000 CL15 @3733 CL16 porque o 5800x não deu boot quando botei 1900mhz 1:1 aí nem quis fuçar mas reduzi alguns subtimings depois, acho que é até mais importante mexer nos subtimings que só a frequência e o tCL e timings primários, mas mexer em RAM é chato pra krl kkkkkk, e agora como migrei pra 4k também não faz mais sentido bater cabeça com isso com a GPU atual

Memória é um saco pra mexer mesmo..

Aqui ta assim:

ou seja e o mesmo "HT link" que tem nos Ryzens ?

então pra fazer over tem que ficar de olho pra ver se não fica 2:1 etc... ?

se sim mais uma coisa pra complicar o oc

Desse InfinityLink não se tem nenhuma informação, por isso não tenho nem como responder vocês. O que se sabe é que o total do tráfego é de 5,3TB/s, mas nem sabemos se esse valor é por chiplet ou o total da soma deles. Mas talvez nem dê para configurarmos ou saber a proporção, pois segundo o que foi informado ao Anandtech o objetivo desse link é ser transparente.que legal, então assim como nos ryzen´s será mais negócio over no IL do que subir a frequência do chip?

---

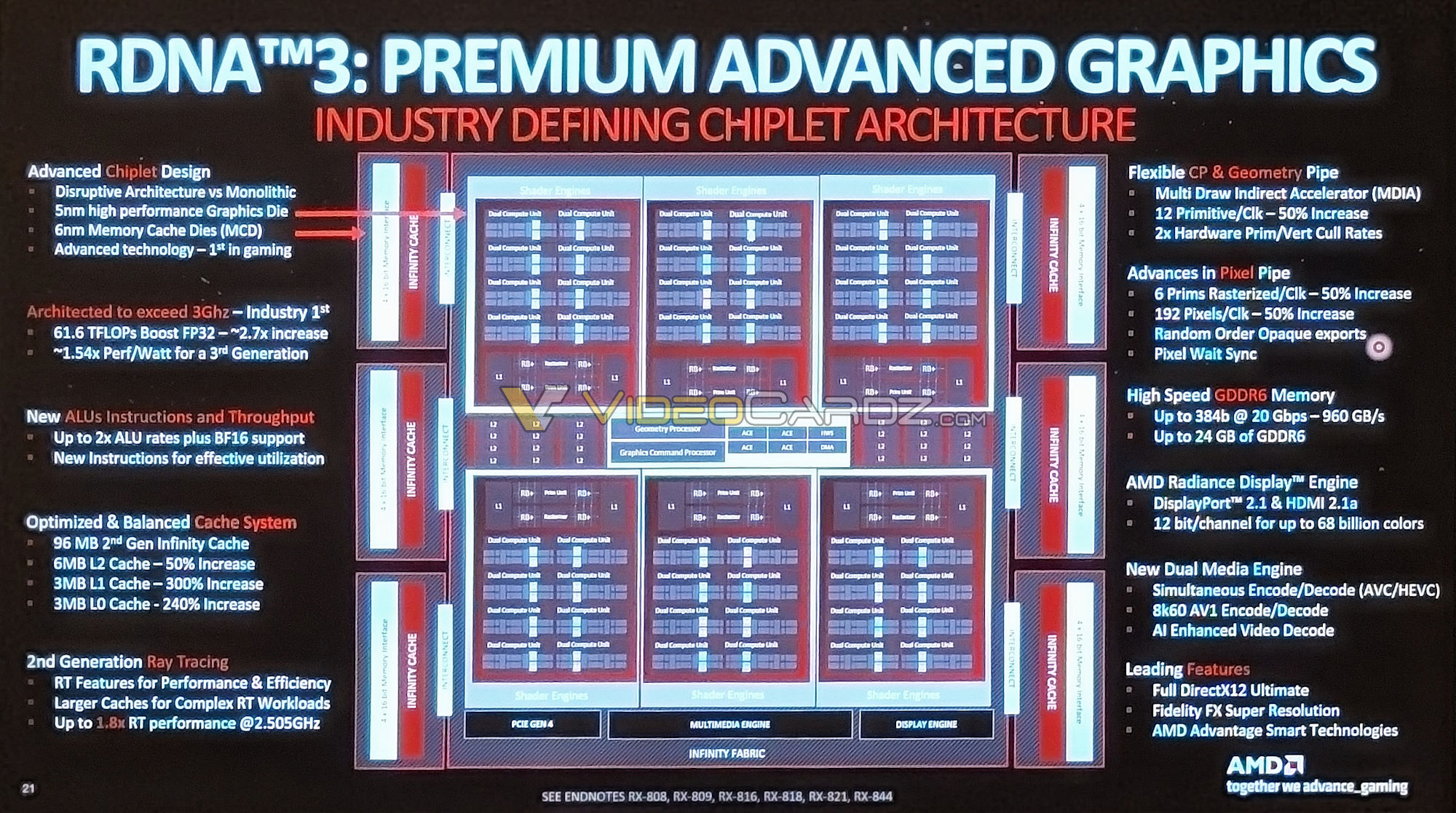

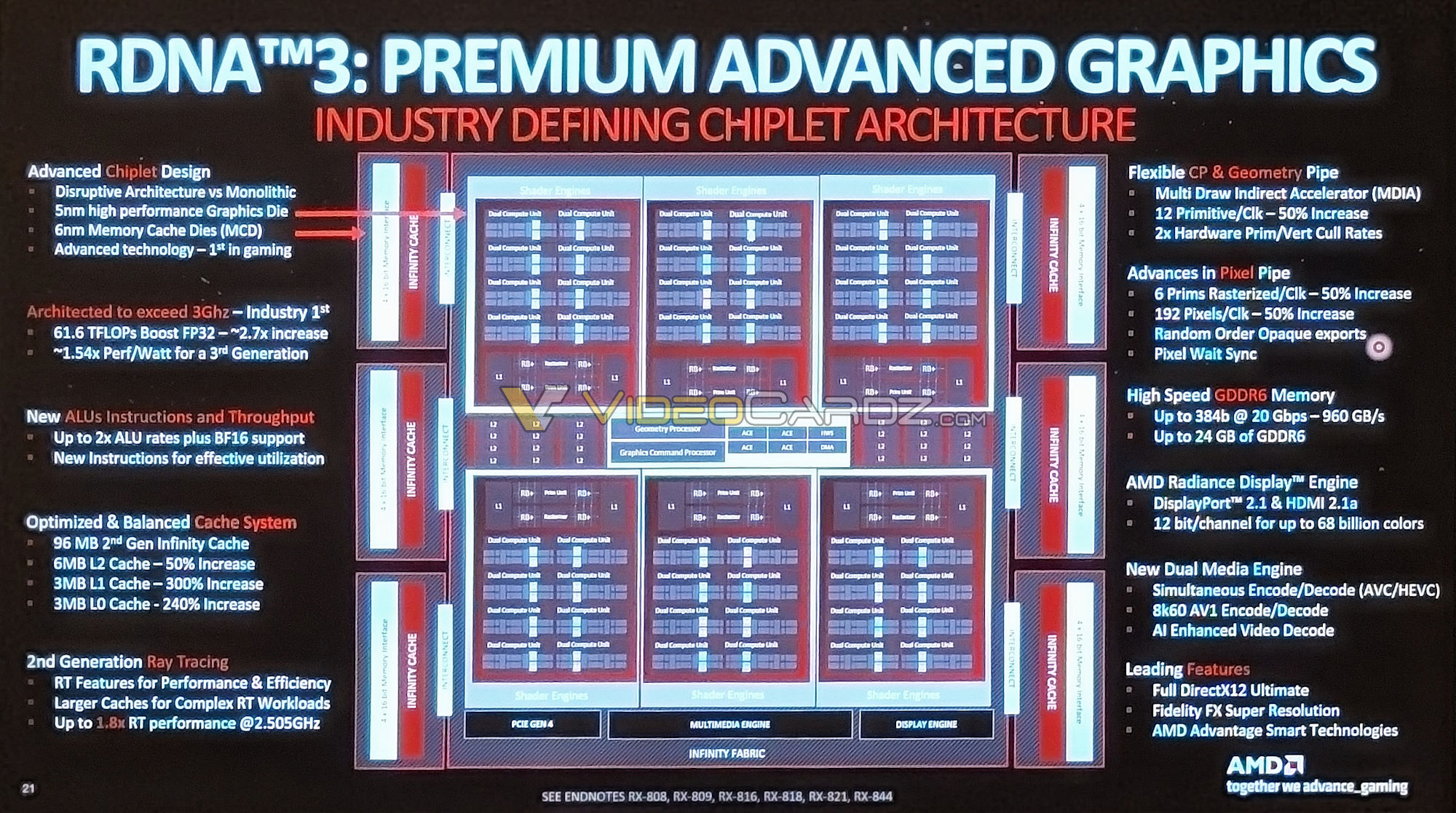

Alleged AMD Navi 31 GPU block diagram leaks out - VideoCardz.com

AMD RDNA3 architecture ‘to exceed 3 GHz’ We received a picture showing the new Navi 31 GPU block diagram. AMD Navi 31 GPU is a chiplet design with one GCD (Graphics Compute Die) and six Memory Cache Dies (MCDs). The outer dies house dual 32-bit memory controllers each, combined with large L3...

É, esse diagrama de bloco traz muita informação boa, e tem uma frase bem incômoda também: "Arquitetada para exceder os 3GHz".

Depois toco nessa linha, antes vamos às diferenças que não sabíamos até agora:

- De 1,25MB para 3MB de cache L0 (+240%)

- De 1MB para 3MB de cache L1 (+300%)

- De 4MB para 6MB de cache L2 (+50%)

- Até 80% de ganho no RTRT à 2.5GHz

- MDIA (Acelerador Indireto de Múltiplas Chamadas)

- De 8 para 12 primitivos por clock na unidade geométrica (+50%)

- Dobro de vazão de culling de primitivos/vértice via hardware

- De 4 para 6 primitivos por clock na unidade de rasterização (+50%)

- De 128 para 192 pixel/clock (+50%)

- ROOE (o que o Angstronomics chamou de OREO)

- Sincronização de espera de pixels

- PCI-Express Gen4

Agora sim, aquela linha dos 3GHz: Muito se falou nos vazamentos da RDNA3 alcançar 3GHz e até o momento a única coisa que vem à cabeça para o decoupling e "apenas" 2.5GHz é justamente o consumo. Ficou claro por essa imagem do diagrama de bloco que mesmo informando sobre os 3GHz todos os números de desempenho são em cima de 2.5GHz (1,8x de RTRT, 2,7x de desempenho, 1,54x de perf/watt, ~61TFlops). Então o que dá para concluir aqui é que simplesmente a AMD limitou o clock para se encaixar nos 54% de ganho performance/watt em cima da geração anterior, e não extrapolar dois conectores de 8-pin de consumo. Somem isso ao consumo da intercomunicação GCD<->MCD e veremos que um clock mais alto impacta pesadamente o consumo (nesse ponto da comunicação mesmo, seriam mais de 100W do InfinityLink caso o clock da GPU fosse de 2.8GHz, então em 3GHz só ela consumiria quase 1/3 de todo o TDP atual da placa).

Não estou descartando outras possibilidades, mas pelo que temos essa é a resposta que me vem à cabeça. Agora vem uma pergunta séria: Não seria melhor investir novamente no HBM ao invés dessa separação MCD+InfCache? O custo dessa memória empilhada é tão impactante ao ponto da AMD preferir esse design chiplet? Estava colocando aqui na balança os dois e não cheguei a uma conclusão =S

Última edição:

Com base no que você explicou, seria possível então as placas das parceiras com 3 conectores romperem a barreira dos 3GHz aumentando o consumo da placa? E se sim, de quanto seria o ganho nesta frequência VS o 2,5GHz?Desse InfinityLink não se tem nenhuma informação, por isso não tenho nem como responder vocês. O que se sabe é que o total do tráfego é de 5,3TB/s, mas nem sabemos se esse valor é por chiplet ou o total da soma deles. Mas talvez nem dê para configurarmos ou saber a proporção, pois segundo o que foi informado ao Anandtech o objetivo desse link é ser transparente.

---

Alleged AMD Navi 31 GPU block diagram leaks out - VideoCardz.com

AMD RDNA3 architecture ‘to exceed 3 GHz’ We received a picture showing the new Navi 31 GPU block diagram. AMD Navi 31 GPU is a chiplet design with one GCD (Graphics Compute Die) and six Memory Cache Dies (MCDs). The outer dies house dual 32-bit memory controllers each, combined with large L3...videocardz.com

É, esse diagrama de bloco traz muita informação boa, e tem uma frase bem incômoda também: "Arquitetada para exceder os 3GHz".

Depois toco nessa linha, antes vamos às diferenças que não sabíamos até agora:

- 1,25MB para 3MB de cache L0 (+240%)

- 1MB para 3MB de cache L1 (+300%)

- 4MB para 6MB de cache L2 (+50%)

- 80% de ganho no RTRT à 2.5GHz

- MDIA (Acelerador Indireto de Múltiplas Chamadas)

- 8 para 12 primitivos por clock na unidade geométrica (+50%)

- Dobro de vazão de primitivos por vértice via hardware

- 4 para 6 primitivos por clock na unidade de rasterização (+50%)

- 144 para 192 pixel/clock (+50%)

- ROOE (o que o Angstronomics chamou de OREO)

- Sincronização de espera de pixels

Agora sim, aquela linha dos 3GHz: Muito se falou nos vazamentos da RDNA3 alcançar 3GHz e até o momento a única coisa que vem à cabeça para o decoupling e "apenas" 2.5GHz é justamente o consumo. Ficou claro por essa imagem do diagrama de bloco que mesmo informando sobre os 3GHz todos os números de desempenho são em cima de 2.5GHz (1,8x de RTRT, 2,7x de desempenho, 1,54x de perf/watt, ~61TFlops). Então o que dá para concluir aqui é que simplesmente a AMD limitou o clock para se encaixar nos 54% de ganho performance/watt em cima da geração anterior, e não extrapolar dois conectores de 8-pin de consumo. Somem isso ao consumo da intercomunicação GCD<->MCD e veremos que um clock mais alto impacta pesadamente o consumo (nesse ponto da comunicação mesmo, seriam mais de 100W do InfinityLink caso o clock da GPU fosse de 2.8GHz, então em 3GHz só ela consumiria quase 1/3 de todo o TDP atual da placa).

Não estou descartando outras possibilidades, mas pelo que temos essa é a resposta que me vem à cabeça. Agora vem uma pergunta séria: Não seria melhor investir novamente no HBM ao invés dessa separação MCD+InfCache? O custo dessa memória empilhada é tão impactante ao ponto da AMD preferir esse design chiplet? Estava colocando aqui na balança os dois e não cheguei a uma conclusão =S

Pensei nisso com base na placa 7900XTX da ASUS que irá utilizar a mesma carcaça da RTX 4090.

Assim, não é uma certeza, é apenas a minha conclusão com o que temos. E enquanto esse slide dê a entender essa possibilidade, "ser arquitetado para" é diferente de conseguir, tanto que...Com base no que você explicou, seria possível então as placas das parceiras com 3 conectores romperem a barreira dos 3GHz aumentando o consumo da placa? E se sim, de quanto seria o ganho nesta frequência VS o 2,5GHz?

Pensei nisso com base na placa 7900XTX da ASUS que irá utilizar a mesma carcaça da RTX 4090.

Segundo essa informação, são 12% a mais de clock (2,5GHz -> 2,8GHz) para um ganho de meros 5% no TSE (se olharmos pelo "game clock" de 2,3GHz então são 21% a mais de clock). É um retorno pequeno para o grande aumento de consumo (355W -> 450W), indicando que ou a RDNA não escala bem acima dos 80CUs (o limite das GCN era de 60CUs) ou está havendo um gargalo que pode ser o front-end, a intercomunicação ou a largura de banda. Se for o front faz sentido a placa ter um clock ~9% maior nele que nos shaders, já se for a intercomunicação não sei se será possível configurá-la (possivelmente não, tal qual é hoje na RDNA2), mas dará para descobrir isso com as Navi33 que serão monolíticas (logo uma variável a menos).

Tem também o limite da vBIOS e do driver, se um ou outro (ou ambos) oferecerem uma margem pequena nada poderá ser feito, por mais que as AIBs empurrem os coolers da RTX4090 nas 7900XTX isso não mudará, só teremos placas mais frias e desnecessariamente grandes.

---

E quanto à essa outra informação aqui... vou deixar até dentro do spoiler pois é naquele clássico caso de "ouvi de uma AIB desconhecida em um fórum chinês...", então não estou muito afim de dar total credibilidade a ela não, apenas informando aqui uma possibilidade.

Última edição:

Prezados, e alguém aqui tem uma 6950xt, 6900xt ou 6800xt?

Eu gostaria de saber, na real, como está a estabilidade delas no último ano.

Ainda tem alguma tela azul? Congelamentos? Falta de fluidez?

Qual prefeririam, uma 7900xfx ou 3090ti (só pra sair da AMD)?

Me dá a real, por favor.

6800XT desde o lançamento praticamente, modelo reference da Asus. Uso o pc diariamente e zerei uns 40-50 jogos nesse tempo (uns 2 anos). Bastante coisa em dx11, vários indies tb. No geral, não lembro de problemas que tive. Maior parte do tempo joguei em tela de 1440p 155hz, alguns jogos em 4k 120hz.

Não joguei nenhum título que eu lembro que usava RT, só o Shadow of Tomb Raider que tem nas sombras apenas.

Pra não dizer que tive zero problemas, esses dias a tela do monitor principal (uso 2) ficou verde e travou. Reiniciei, reabri tudo liguei o over na placa e momentos depois, travou de novo. Reiniciei novamente. Não sei se é relacionado a gpu ou meu windows, mas depois que desabilitei o over na placa (que uso desde que peguei ela, pelo adrenalin mesmo) não ocorreram mais. As 2 ocorrências foram mexendo no Edge. Talvez seja instabilidade desses valores do meu over com o driver mais recente (eu atualizo sempre que sai algum novo, inclusive os opcionais).

Em jogos mesmo, nunca tive problemas.

Assim, não é uma certeza, é apenas a minha conclusão com o que temos. E enquanto esse slide dê a entender essa possibilidade, "ser arquitetado para" é diferente de conseguir, tanto que...

Segundo essa informação, são 12% a mais de clock (2,5GHz -> 2,8GHz) para um ganho de meros 5% no TSE (se olharmos pelo "game clock" de 2,3GHz então são 21% a mais de clock). É um retorno pequeno para o grande aumento de consumo (355W -> 450W), indicando que ou a RDNA não escala bem acima dos 80CUs (o limite das GCN era de 60CUs) ou está havendo um gargalo que pode ser o front-end, a intercomunicação ou a largura de banda. Se for o front faz sentido a placa ter um clock ~9% maior nele que nos shaders, já se for a intercomunicação não sei se será possível configurá-la (possivelmente não, tal qual é hoje na RDNA2), mas dará para descobrir isso com as Navi33 que serão monolíticas (logo uma variável a menos).

Tem também o limite da vBIOS e do driver, se um ou outro (ou ambos) oferecerem uma margem pequena nada poderá ser feito, por mais que as AIBs empurrem os coolers da RTX4090 nas 7900XTX isso não mudará, só teremos placas mais frias e desnecessariamente grandes.

---

E quanto à essa outra informação aqui... vou deixar até dentro do spoiler pois é naquele clássico caso de "ouvi de uma AIB desconhecida em um fórum chinês...", então não estou muito afim de dar total credibilidade a ela não, apenas informando aqui uma possibilidade.

Se acharem uma forma de empurrar acima de 3GHz de forma estável e sem exigir um aumento de consumo grande vai ser interessante desde que os ganhos em desempenho compensem.

Assim, não é uma certeza, é apenas a minha conclusão com o que temos. E enquanto esse slide dê a entender essa possibilidade, "ser arquitetado para" é diferente de conseguir, tanto que...

Segundo essa informação, são 12% a mais de clock (2,5GHz -> 2,8GHz) para um ganho de meros 5% no TSE (se olharmos pelo "game clock" de 2,3GHz então são 21% a mais de clock). É um retorno pequeno para o grande aumento de consumo (355W -> 450W), indicando que ou a RDNA não escala bem acima dos 80CUs (o limite das GCN era de 60CUs) ou está havendo um gargalo que pode ser o front-end, a intercomunicação ou a largura de banda. Se for o front faz sentido a placa ter um clock ~9% maior nele que nos shaders, já se for a intercomunicação não sei se será possível configurá-la (possivelmente não, tal qual é hoje na RDNA2), mas dará para descobrir isso com as Navi33 que serão monolíticas (logo uma variável a menos).

Tem também o limite da vBIOS e do driver, se um ou outro (ou ambos) oferecerem uma margem pequena nada poderá ser feito, por mais que as AIBs empurrem os coolers da RTX4090 nas 7900XTX isso não mudará, só teremos placas mais frias e desnecessariamente grandes.

---

E quanto à essa outra informação aqui... vou deixar até dentro do spoiler pois é naquele clássico caso de "ouvi de uma AIB desconhecida em um fórum chinês...", então não estou muito afim de dar total credibilidade a ela não, apenas informando aqui uma possibilidade.

Tudo depende de qto a placa vai entregar em performance. Se usarmos 1.5x como media em relação a 6950. A placa vai entregar 139 fps de média em 4k(techpowerup) oq seria 9% a menos que a 4090 e tranquilamente uns 10-15% acima da 4080.

6800XT desde o lançamento praticamente, modelo reference da Asus. Uso o pc diariamente e zerei uns 40-50 jogos nesse tempo (uns 2 anos). Bastante coisa em dx11, vários indies tb. No geral, não lembro de problemas que tive. Maior parte do tempo joguei em tela de 1440p 155hz, alguns jogos em 4k 120hz.

Não joguei nenhum título que eu lembro que usava RT, só o Shadow of Tomb Raider que tem nas sombras apenas.

Pra não dizer que tive zero problemas, esses dias a tela do monitor principal (uso 2) ficou verde e travou. Reiniciei, reabri tudo liguei o over na placa e momentos depois, travou de novo. Reiniciei novamente. Não sei se é relacionado a gpu ou meu windows, mas depois que desabilitei o over na placa (que uso desde que peguei ela, pelo adrenalin mesmo) não ocorreram mais. As 2 ocorrências foram mexendo no Edge. Talvez seja instabilidade desses valores do meu over com o driver mais recente (eu atualizo sempre que sai algum novo, inclusive os opcionais).

Em jogos mesmo, nunca tive problemas.

Qual monitor/tv você usa? Joga em HDR?

Tudo depende de qto a placa vai entregar em performance. Se usarmos 1.5x como media em relação a 6950. A placa vai entregar 139 fps de média em 4k(techpowerup) oq seria 9% a menos que a 4090 e tranquilamente uns 10-15% acima da 4080.

Desempenho da 4080 promete ser bizarramente inferior a 4090 em alguns jogos..

Então eu não ficaria surpreso se a 7900xtx ficasse 30~50% acima dela em raster

Slide da nvidia...surra de 92,57%

--- Post duplo é unido automaticamente: ---

EDIT

E o pior de tudo ainda.. A 4080 apenas 45% acima da 3080, custando 70% mais.

Isso é uma PIADA.

Tomara q o jaquetinha se fod4 com força... o nível de sacanagem nao tem precedentes

Última edição:

Se a 7900 XTX conseguir se aproximar mto da 4090 custando 999 (que eu já tinha cantado bola antes, hein!) será a melhor placa para entusiastas em questão de performance x preço.

Qual monitor/tv você usa? Joga em HDR?

Maior parte do tempo jogo no monitor S2719DGF da Dell (QHD 155hz, freesync sem HDR). Quando jogo na tv é uma Q70T (4k 120hz freesync com HDR).

Se a 7900 XTX conseguir se aproximar mto da 4090 custando 999 (que eu já tinha cantado bola antes, hein!) será a melhor placa para entusiastas em questão de performance x preço.

Tenho até medo dos preços das lojas BR haha

se for acima de 8500 é roubo

Tenho até medo dos preços das lojas BR haha

se for acima de 8500 é roubo

8500? Não acho que venha nesse valor, deve vir por uns 10k mesmo. Se a 4090 custa 1600 lá e aqui tá custando 16000, então 999 = 9999, não?

Se essa tabela for verdade a AMD meio que desistiu de competir com RT ON.

Isso explicaria muita coisa tb desses lançamentos.

Gosta de graficos bonitos cheio de efeito vai de Nvidia se prefere força bruta de AMD.

Pode até ter desistido, mas dps que ver a própria Intel dando uma paulada nela na segunda geração de placas isso muda rapidinho.

Se essa tabela for verdade a AMD meio que desistiu de competir com RT ON.

Isso explicaria muita coisa tb desses lançamentos.

Gosta de graficos bonitos cheio de efeito vai de Nvidia se prefere força bruta de AMD.

por que a amd tem que ficar correndo atrás de algo proprietário

Se essa tabela for verdade a AMD meio que desistiu de competir com RT ON.

Isso explicaria muita coisa tb desses lançamentos.

Gosta de graficos bonitos cheio de efeito vai de Nvidia se prefere força bruta de AMD.

deixa isso pra la e faz um de código livre algo suportado em meia dúzia de jogos não vale o investimento

Tem várias observações a ser dito sobre essa tabela, ela é apenas para mostrar por alto a vazão de ray-triangle, que no fim das contas não condiz com a realidade (a 4090 não é 4x mais rápida que a 3090Ti em RTRT, com a tabela dá a entender). Várias outras instruções e processamento entram no pipeline do próprio RTRT, esse número é apenas o resultado de "SM * clock * interseções por ciclo".

Se essa tabela for verdade a AMD meio que desistiu de competir com RT ON.

Isso explicaria muita coisa tb desses lançamentos.

Gosta de graficos bonitos cheio de efeito vai de Nvidia se prefere força bruta de AMD.

Desse InfinityLink não se tem nenhuma informação, por isso não tenho nem como responder vocês. O que se sabe é que o total do tráfego é de 5,3TB/s, mas nem sabemos se esse valor é por chiplet ou o total da soma deles. Mas talvez nem dê para configurarmos ou saber a proporção, pois segundo o que foi informado ao Anandtech o objetivo desse link é ser transparente.

É total... eles mencionam na apresentação que é 2 e poucos vezes mais rápido que a concorrência. No caso era o UltraFusion com 2.5TB/s.

O IF de 3 geração chega a 800gb/s, passar pra 5.3ghz é um balo avanço, é tipo 800 e pouco Gb/s pra cada CCD.

Queria saber mesmo é se a velocidade escala com a quantidade, porque se for isso, na 7800XT a velocidade seria menor 3.5TB/s.

Agora sim, aquela linha dos 3GHz: Muito se falou nos vazamentos da RDNA3 alcançar 3GHz e até o momento a única coisa que vem à cabeça para o decoupling e "apenas" 2.5GHz é justamente o consumo. Ficou claro por essa imagem do diagrama de bloco que mesmo informando sobre os 3GHz todos os números de desempenho são em cima de 2.5GHz (1,8x de RTRT, 2,7x de desempenho, 1,54x de perf/watt, ~61TFlops). Então o que dá para concluir aqui é que simplesmente a AMD limitou o clock para se encaixar nos 54% de ganho performance/watt em cima da geração anterior, e não extrapolar dois conectores de 8-pin de consumo. Somem isso ao consumo da intercomunicação GCD<->MCD e veremos que um clock mais alto impacta pesadamente o consumo (nesse ponto da comunicação mesmo, seriam mais de 100W do InfinityLink caso o clock da GPU fosse de 2.8GHz, então em 3GHz só ela consumiria quase 1/3 de todo o TDP atual da placa).

Tem aquele rumor do Twitter que os AIBs estão conseguindo só 3% de overclock headroom com a Bios atual, talvez melhore até o lançamento.

A Asus até agora não comentou nada dos clocks da TUF e se não subir mto, não vai ter Strix.

HBM ainda é controlada pela carissima Rambus então foram na terceira melhor opção.Não estou descartando outras possibilidades, mas pelo que temos essa é a resposta que me vem à cabeça. Agora vem uma pergunta séria: Não seria melhor investir novamente no HBM ao invés dessa separação MCD+InfCache? O custo dessa memória empilhada é tão impactante ao ponto da AMD preferir esse design chiplet? Estava colocando aqui na balança os dois e não cheguei a uma conclusão =S

Queria mesmo é ver os ganhos se pelo menos na 7900 XT tivesse a DDR6X (segunda melhor opção). Olha o gás que esse memo está dando na 3060 Ti.

E a Samsung já anunciou a DDR7, provavelmente a série 5 da Nvadia vai usar já, é a única empresa que consegue os melhores deals tanto com a Samsung como com a Micron.

8500? Não acho que venha nesse valor, deve vir por uns 10k mesmo. Se a 4090 custa 1600 lá e aqui tá custando 16000, então 999 = 9999, não?

4090 teve desde o lançamento por 12800 no kabum, os modelos mais baratos.

Com cupom e prime saiu por 11800..

Tomara q nao enfiem a faca.. vamos ver..

Users who are viewing this thread

Total: 8 (membros: 5, visitantes: 3)